Dodatkowy układ laboratoryjny nr 1

W laboratorium znajduje się dodatkowy układ laboratoryjny z płytką XS40 rozszerzoną o tekstowy wyświetlacz LCD z klawiaturą, 2 przetworniki C/A, 1 przetwornik A/C z multiplekserem analogowym, uniwersalne wejście i wyjście cyfrowe (z zabezpieczeniem) oraz głośniczek piezo.

Wyżej wymienione rozszerzenia nie zmieniają następujących funkcji płytki XS40: wyświetlacz LED i wyjście VGA, komunikacja z PC przez port równoległy.

Można nadal korzystać z mikrokontrolera i pamięci statycznej ale należy odpowiednio sterować sygnałem CSIO. Standardowy test płytki działa bez zmian.

Poniżej podano funkcjonalny opis poszczególnych modułów rozszerzeń.

1.

EKSPANDER MAGISTRALI:

Aby umożliwić podłączenie wielu urządzeń I/O konieczne było wykorzystanie dwukierunkowej magistrali danych i sterującej. Magistrale te wraz z układami pośredniczącymi są zaimplementowane na płycie pośredniczącej do której włożona jest płyta XS40.

Uwaga ! Płytka XS40 powinna być wkładana do płyty pośredniczącej tak aby złącze portu równoległego do PC znajdowało się z lewej strony. Należy także pamiętać o podłączeniu do płyty pośredniczącej napięcia +8V (dodatkowy czerwony kabelek z płytki XS40).

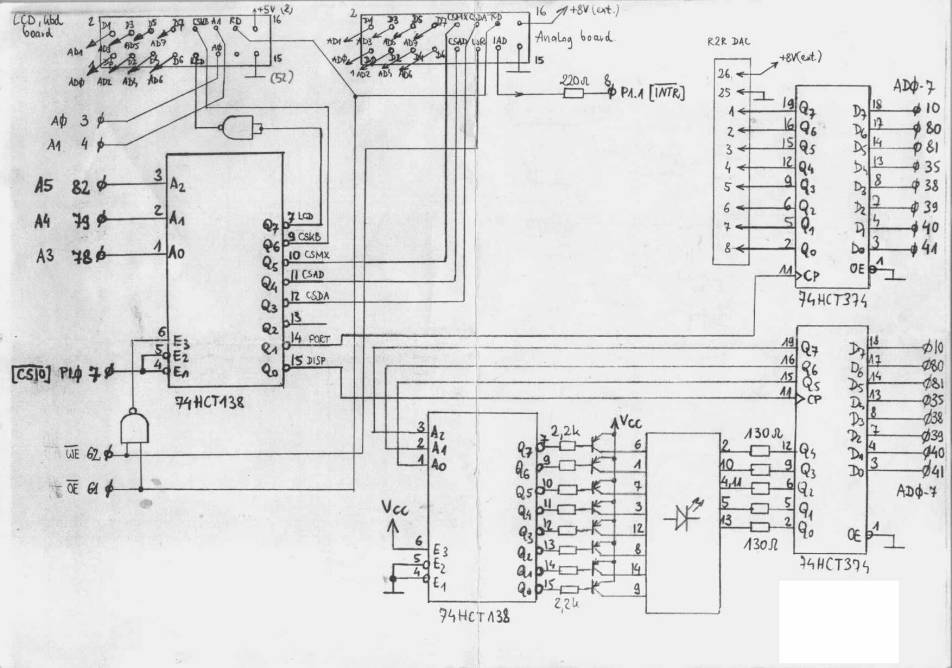

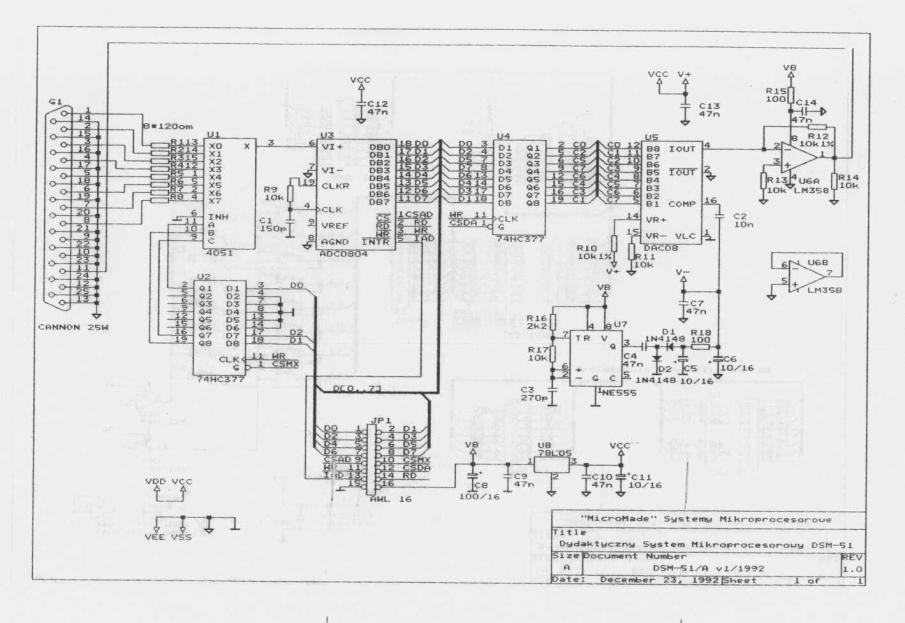

Poniżej podano schemat płyty pośredniczącej:

Plik UCF dla modułów rozszerzeń jest następujący:

# 12 MHz clock:

net clk loc=p13;

# system reset (port D0):

net rst loc=p44;

# address bus:

net a0 loc=p3;

net a1 loc=p4;

net a3 loc=p78;

net a4 loc=p79;

net a5 loc=p82;

# control bus:

net we loc=p62;

net oe loc=p61;

net csio loc=p7;

# data bus:

net data<0> loc=p41;

net data<1> loc=p40;

net data<2> loc=p39;

net data<3> loc=p38;

net data<4> loc=p35;

net data<5> loc=p81;

net data<6> loc=p80;

net data<7> loc=p10;

# interrupt from A/D converter:

net intr loc=p8;

# external input and output:

net ext_in loc=p6;

net ext_out loc=p9;

# buzzer:

net buz loc=p77;

# disable RAM and CPU:

net cpu_rst loc=p36;

net ram_cs loc=p65;

Na magistralę składają się następujące sygnały:

A0,A1 – linie adresowe używane wyłącznie do wyboru rejestrów LCD i klawiatury.

A3,A4,A5 – linie adresowe wyboru modułu I/O.

(linia A2 i linie A6-A15 są nieużywane).

AD0-AD7 – linie danych (dwukierunkowe) (w zbiorze UCF magistrala ma nazwę data).

WE, OE – sygnały kontrolne (aktywne poziomem niskim).

Wyżej wymienione sygnały są współdzielone z pamięcią SRAM i mikrokontrolerem.

Do rozróżnienia czy komunikacja odbywa się z pamięcią SRAM/mikrokontrolerem czy też z modułami I/O wprowadzono dodatkowy sygnał: CSIO. Niski poziom tego sygnału włącza dekoder adresowy dodatkowych urządzeń I/O, wysoki poziom powoduje ich wyłączenie. Pamięć SRAM w ten sam sposób jest sterowana przez sygnał RAM_CS. Jeżeli nie będziemy korzystać ani z mikrokontrolera ani z pamięci SRAM powinniśmy sygnał RAM_CS ustawić na poziomie logicznym „1”, zaś sygnał CSIO na poziomie logicznym „0”. Ważne jest też zablokowanie pracy mikrokontrolera (jeżeli z niego nie korzystamy) ustawiając sygnał CPU_RST na poziom „1”.

Opis protokołu komunikacyjnego (zapis do urządzenia I/O):

Opis protokołu komunikacyjnego (odczyt z urządzenia I/O):

Czasy przedstawione na wykresie zależą od urządzenia I/O z którym prowadzona jest komunikacja.

Dla rejestrów 74HC541, 74HCT374, 74HC377 można przyjąć następujące bezpieczne wartości:

tsetup

= 1 clk tenable = 1

clk thold = 1 clk tready = 0,5 clk tdisable = 0,5 clk (clk = 83 ns jest to okres zegara 12 MHz)

dotyczy to komunikacji z: PORT (portem równoległym), DISP (wyświetlaczem mozaikowym), CSMX (multiplekserem analogowym wejścia przetwornika A/C), CSDA (przetwornikiem C/A), CSKB (dodatkową klawiaturą).

Dla komunikacji z CSAD (przetwornik A/C: ADC0804 firmy Intersil):

tsetup

= 1 clk tenable = 3

clk thold = 1 clk tready = 2,5 clk tdisable = 3 clk (clk = 83 ns jest to okres zegara 12 MHz)

Dla komunikacji z wyświetlaczem LCD:

tsetup

= 2 clk tenable = 6

clk thold = 1 clk tready = 5 clk tdisable = 3 clk tcycle = 12 clk (clk = 83 ns jest to okres zegara 12 MHz)

Dodatkowe wskazówki:

Parametry czasowe komunikacji z LCD (najbezpieczniejsze) można także oczywiście stosować do komunikacji z pozostałymi urządzeniami).

2.

PORT RÓWNOLEGŁY:

Port ten sterowany jest z wyjścia Q1 dekodera adresowego (adres: 001xxx). Dodatkowy port równoległy może mieć wiele zastosowań. W przykładowej płytce dołączono do niego dodatkowy przetwornik C/A typu „drabinka R2R”. Jest on dołączony na dodatkowej małej płytce. Ma rozdzielczość 7 bitów. Zakres zmian napięcia wyjściowego: 0 - 3.3V. Wyjście oznaczone literką Y. Uwaga – wyjście ma stosunkowo dużą impedancję – około 8kW - nie należy stosować dużych obciążeń pojemnościowych.

Najstarszy bit portu wyprowadzono na oddzielne dodatkowe wyjście cyfrowe oznaczone literką Z (np. do wygaszania plamki oscyloskopu), amplituda 5V. Poza tym na dodatkowej płytce znajduje się także wyjście standardowego przetwornika C/A (patrz. p. 7) oznaczone literką X. Oznaczenia te sugerują właściwe podłączenie w przypadku realizacji ćwiczeń z oscyloskopem (w trybie X-Y-Z).

3.

WYŚWIETLACZ MOZAIKOWY:

Wyświetlacz mozaikowy sterowany jest przez zapis do portu DISP (wyjście Q0 dekodera adresowego, adres: 000xxx). Bity b7-b5 wybierają wyświetlaną linię (5 LED). O tym które z tych LED mają być zapalone (bit „0”), a które zgaszone (bit „1”) decydują pozostałe bity: b4– b0. Aby wyświetlić cały napis – trzeba cyklicznie wyświetlać wszystkie linie. Częstotliwość przełączania linii nie powinna przekraczać 10 kHz.

|

|

b4 |

b3 |

b2 |

b1 |

b0 |

|

q7 |

o |

o |

o |

o |

o |

|

q6 |

o |

o |

o |

o |

o |

|

q5 |

o |

o |

o |

o |

o |

|

q4 |

o |

o |

o |

o |

o |

|

q3 |

o |

o |

o |

o |

o |

|

q2 |

o |

o |

o |

o |

o |

|

q1 |

o |

o |

o |

o |

o |

|

q0 |

o |

o |

o |

o |

o |

q(7-0) <= 3to8encoder(b7-b5)

4.

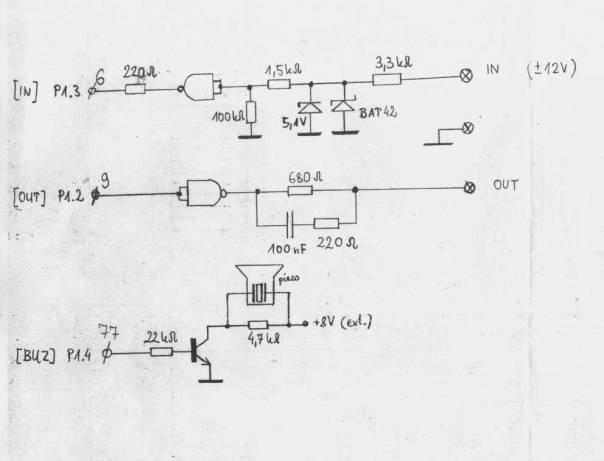

UNIWERSALNE WEJŚCIE CYFROWE:

Wejście cyfrowe jest zabezpieczone, wytrzymuje poziom napięcia RS232: ±12V.

Do końcówki 6 układu XILINX podłączony jest zanegowany sygnał wejścia. Do wejścia można podłączać dowolne przewody dzięki krótkiej listwie zaciskowej. Wejście to może być wykorzystywane przez układ FPGA i mikrokontroler. Wejście cyfrowe może być wykorzystywane do realizacji wejścia RS232 lub np. do pomiarów częstotliwości.

5.

UNIWERSALNE WYJŚCIE CYFROWE:

Wyjście cyfrowe o poziomach logiki TTL. Na wyjściu podany jest zanegowany sygnał z końcówki 9 układu XILINX. Do wyjścia można podłączać dowolne przewody dzięki krótkiej listwie zaciskowej. Wyjście może być wykorzystywane albo przez FPGA albo przez mikrokontroler. Wyjście cyfrowe może być wykorzystane np. do realizacji wyjścia RS232.

6.

GŁOŚNICZEK:

Do końcówki 77 układu FPGA podłączony jest układ z głośniczkiem piezoceramicznym. Jest to stosunkowo cichy głośniczek (bez rezonatora). Może być wykorzystywany przez FPGA albo przez mikrokontroler.

Pozostałe

bloki funkcjonalne znajdują się poza płytką pośredniczącą:

7.

PRZETWORNIKI A/C i C/A:

Przetwornik A/C działa na zasadzie aproksymacji wagowej. Czas konwersji wynosi około 100 ms. Konwersję rozpoczyna się zapisując do portu CSAD (wyjście Q4 dekodera adresowego, adres: 100xxx) dowolną daną (liczy się wystąpienie impulsu WE).

Zakończenie konwersji sygnalizowane jest wystąpieniem niskiego stanu logicznego na wyjściu INTR. Wyjście to jest dołączone do końcówki 8 układu FPGA (może być także wykorzystywane przez mikrokontroler). Ważne jest żeby zacząć sprawdzać stan tego wyjścia 450 ns po rozpoczęciu konwersji (wcześniej może jeszcze być w stanie „0”). Po zakończeniu konwersji można odczytać 8-bitową daną (ten sam port o adresie: 100xxx). Zakres napięcia wejściowego przetwornika: 0 - 5V.

Zanim zaczniemy korzystać z przetwornika A/C należy ustawić za pomocą multipleksera analogowego z którego wejścia chcemy korzystać. W tym celu trzeba zapisać do portu CSMX (wyjście Q5 dekodera adresowego, adres: 101xxx) daną której trzy najmłodsze bity oznaczają numer wejścia. W testowej płytce zainstalowano 2 potencjometry (numery multipleksera: 0 i 1) i dwa wejścia zewnętrzne (kable zakończone wtykami BNC) (numery multipleksera 2 i 3). Pozostałe 4 wejścia multipleksera są niewykorzystane.

Przetwornik C/A (DAC08) realizuje szybką (70 ns) konwersję 8-bitowej danej do sygnału analogowego o zakresie napięcia: 0 – 5 V. Do wykonania konwersji wystarczy zapisać daną do portu CSDA (wyjście Q3 dekodera adresowego, adres: 011xxx). Wyjście jest oznaczone na płytce testowej literką X.

Poniżej przedstawiono schemat modułu z przetwornikami A/C i C/A:

8.

DODATKOWA KLAWIATURA:

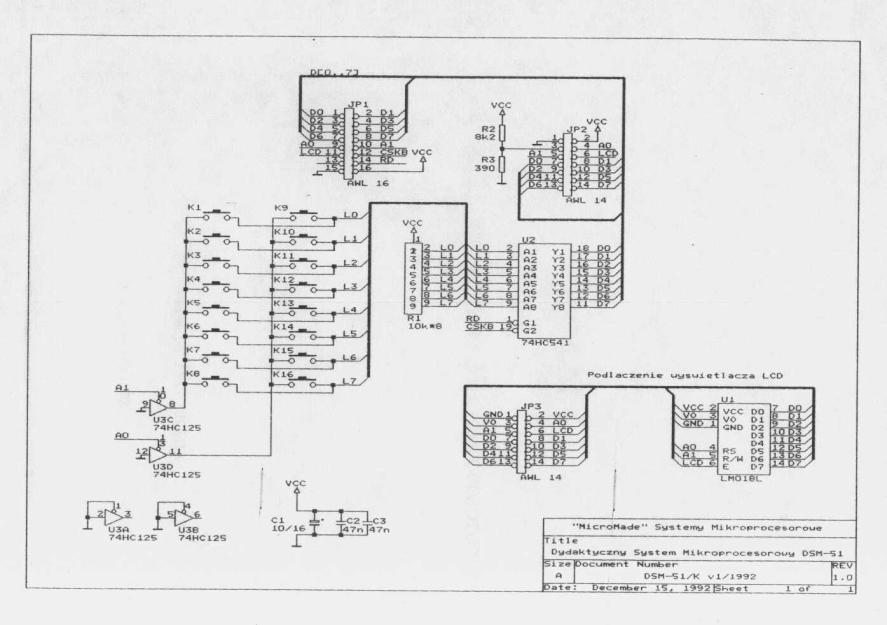

Klawiatura zawiera 16 klawiszy, jest sterowana przez port CSKB (wyjście Q6 dekodera adresowego, adres: 110xxx). W odczycie tego portu ma znaczenie dolna część adresu: A1 i A0). Gdy A0=1, A1=0 wybrany do odczytu jest dolny bank klawiszy (K1-K8). Gdy A0=0, A1=1 wybrany do odczytu jest górny bank klawiszy (K9-K16). Stan klawiszy odczytujemy z wartości odczytanej z portu CSKB – bit AD0 odpowiada klawiszom K1 lub K9, AD1 odpowiada klawiszom K2 lub K10, itd. (0 – klawisz naciśnięty, 1 – klawisz zwolniony).

Należy pamiętać o możliwości drgań zestyków.

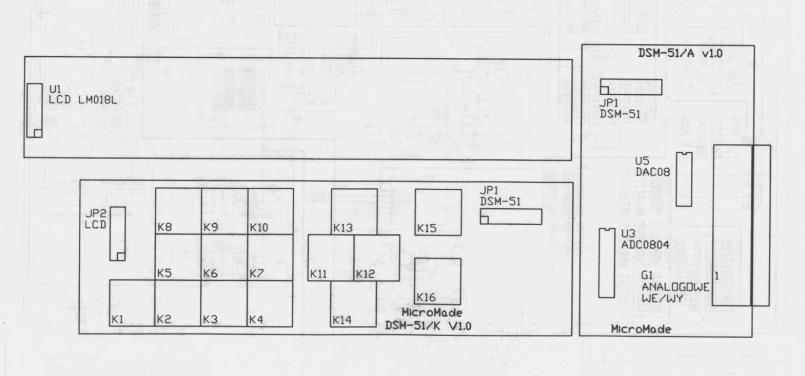

Położenie klawiszy K1-K16 przedstawia następujący rysunek:

Poniżej przedstawiono schemat modułu interfejsu LCD i klawiatury:

9.

WYŚWIETLACZ LCD:

Wyświetlacz LCD sterowany jest przez port LCD (wyjście Q7 dekodera adresowego, adres: 111xxx). W operacjach na tym porcie ma znaczenie dolna część adresu: A1 i A0. Sygnał adresowy A0 podłączony jest do sygnału wyboru rejestru (Register Select – RS) układu LCD.

A0=0 wybiera rejestry sterujące, zaś A0=1 rejestry danych.

Sygnał adresowy A1 podłączony jest do sygnału wyboru zapisu lub odczytu (R/W) – bardzo ważne: zapis do układu LCD może być wykonany tylko przy A1=0 zaś odczyt tylko przy adresie A1=1 (poza tym oczywiście nadal konieczne jest odpowiednie sterowanie sygnałami OE i WE).

Ze względu na to że układ sterujący LCD jest stosunkowo powolny należy pamiętać o odpowiednim wydłużeniu cyklu magistrali przy dostępie do układu LCD (patrz p. 1).

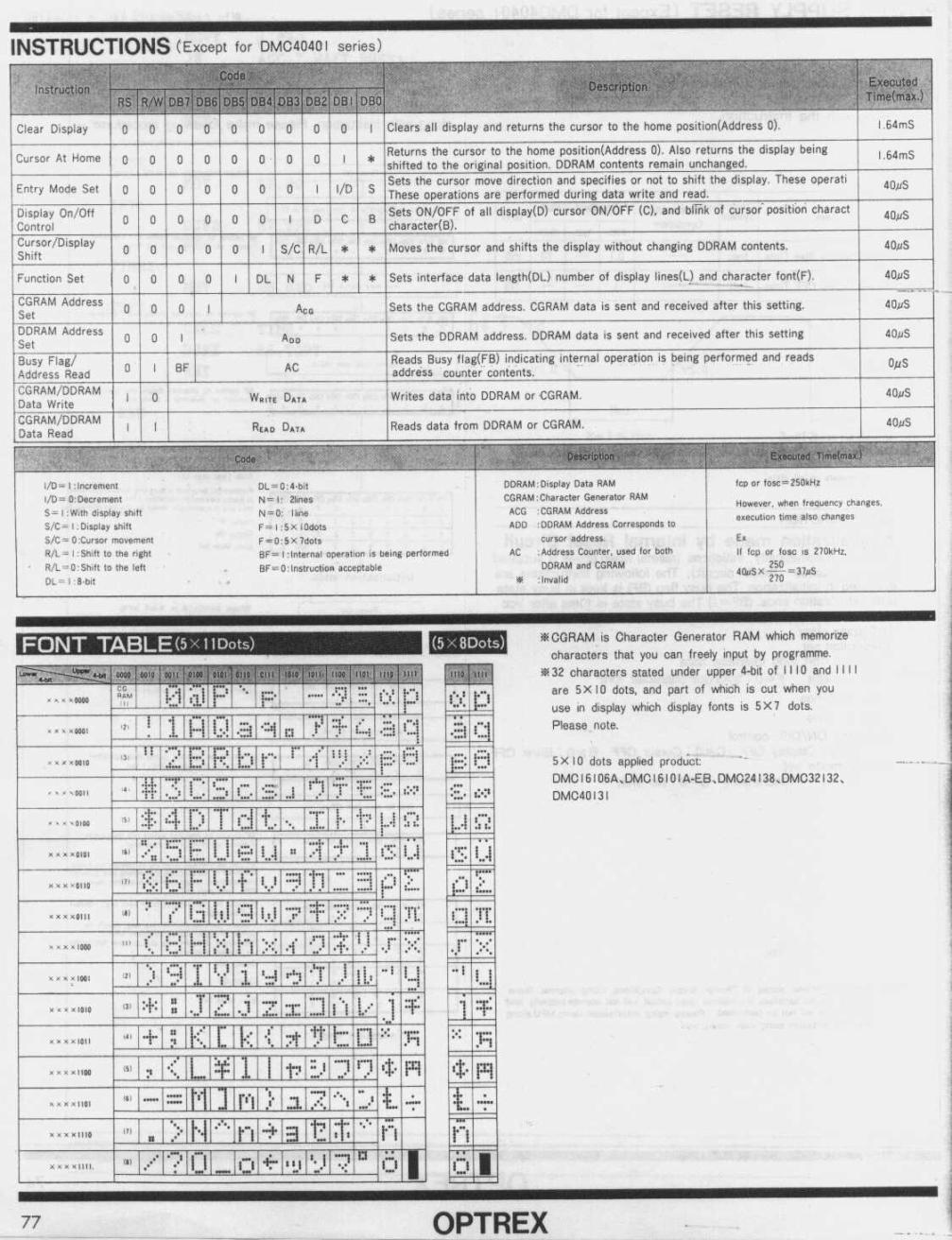

Oprócz tego wykonanie instrukcji sterujących LCD zajmuje dodatkowy czas sterownika co wymaga sprawdzania jego zajętości (flaga BUSY) lub opóźnienia wysłania kolejnych instrukcji o czas określony jako maksymalny czas wykonania instrukcji poprzedniej. Czas ten podany jest w tabeli instrukcji (Executed time max.). Rejestry sterujące można ustawiać według potrzeb, jedyne wymaganie to bit DL (bit sterujący szerokością magistrali danych) który powinien być zawsze ustawiany na 1 (8-bit). Na poniższym rysunku przedstawiono instrukcje sterujące wyświetlaczem LCD:

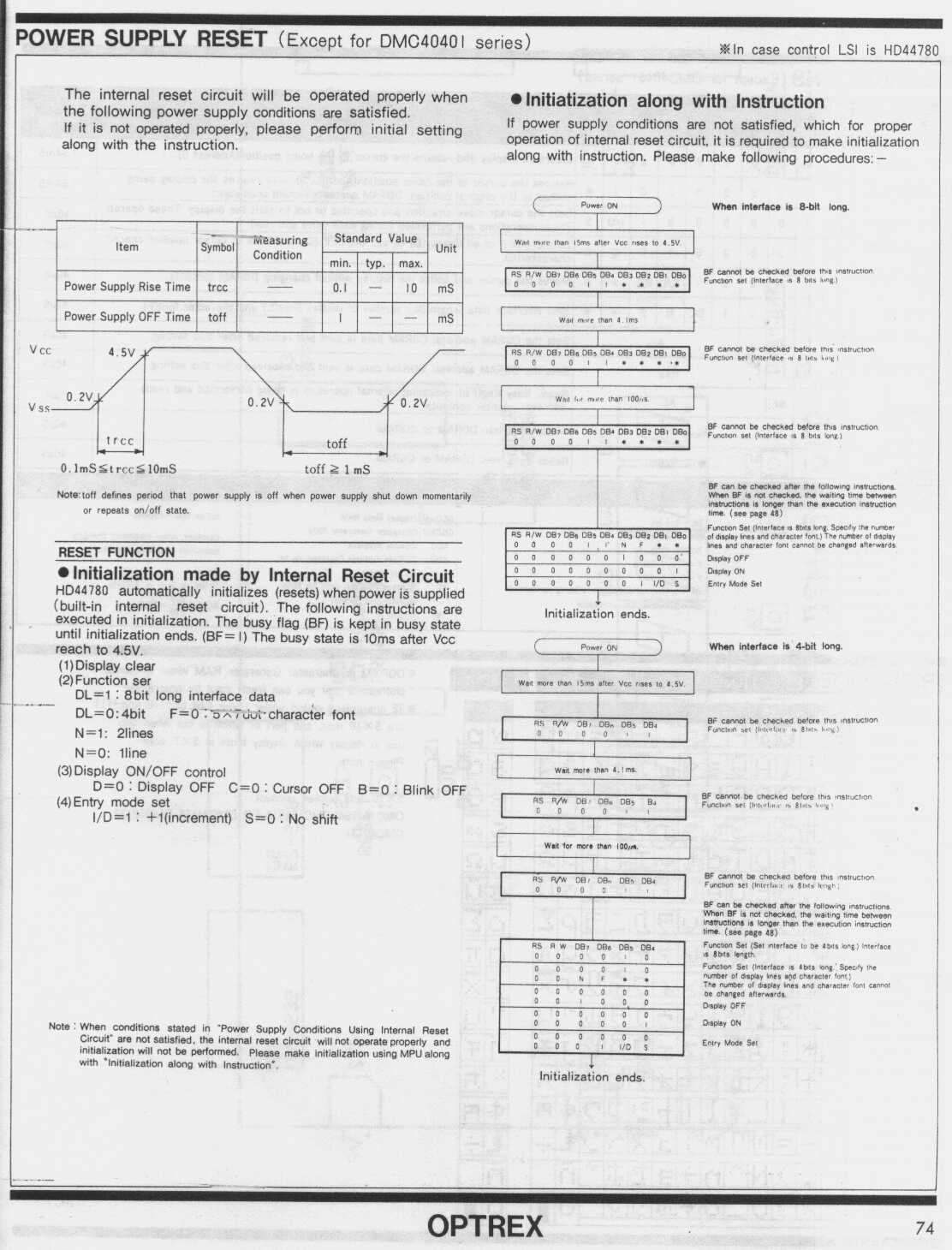

Na poniższym rysunku podano sposób inicjacji sterownika wyświetlacza gdy napięcie zasilające nie spełnia wymagań dla prawidłowego funkcjonowania resetu automatycznego. Podano także początkowe wartości rejestrów po resecie automatycznym.

10.

DODATKI:

Dokumentacja przetworników A/C i C/A:

Dokumentacja mikrokontrolera M80C154S:

Dokumentacja pamięci W24257:

Program

assemblera 8051:

Plik definicji rejestrów mikrokontrolera 80154 (dla assemblera):

Przykładowy plik wejściowy dla assemblera: