Strona główna

|

English version |

Strona główna |

Katedra Systemów Mikroelektronicznych, Wydział Elektroniki, Telekomunikacji i Informatyki, Politechnika Gdańska |

|

| VHDL: | Verilog®: | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

process (clk,rst)

|

always @(posedge clk

or posedge rst)

|

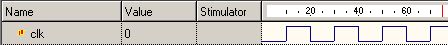

signal clk : std_logic := '0';

...

clk <= not clk after 10ns;

signal we1 : std_logic;

...

we1 <= '0', '1' after 10ns, '0'

after 25ns, '1' after 30ns;

----------- ENTITY A: ------------------------------

library ieee;

use ieee.std_logic_1164.all;

entity a is

port (

a1 : in std_logic;

a2 : in std_logic;

a3 : out std_logic

);

end entity;

architecture beh of a

is

begin

...

end architecture;

----------------------------------------------------

----------- ENTITY B: ------------------------------

library ieee;

use ieee.std_logic_1164.all;

entity b is

port (

b1 : in std_logic;

b2 : in std_logic;

b3 : in std_logic;

b4 : out std_logic

);

end entity;

architecture beh of

b is

signal tmp : std_logic;

component a is

port (

a1 : in std_logic;

a2 : in std_logic;

a3 : out std_logic

);

end component;

begin

X1: a port map (a1 => b1, a2 => b2, a3 => tmp);

X2: a port map (a1 => tmp, a2 => b3, a3 => b4);

end architecture;

----------------------------------------------------