Synteza i Implementacja

Poniższy opis wykonano dla układu opisanego schematem

"moj_schemat.sch". Dla układów opisanych w języku HDL procedura jest

taka sama.

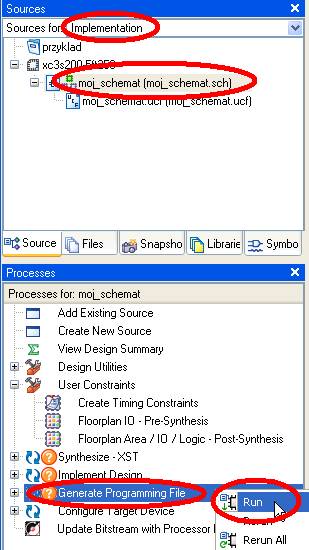

Przełączyć

system ISE w tryb implementacji:

![]()

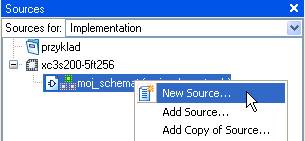

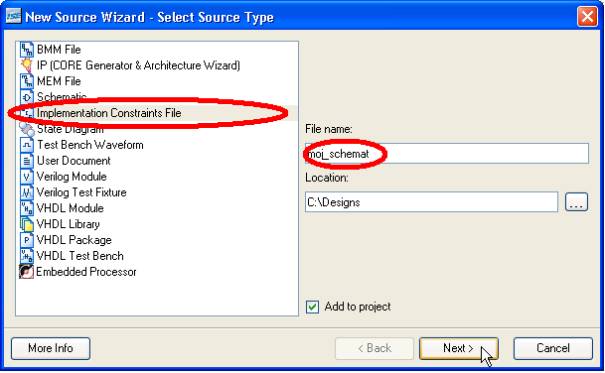

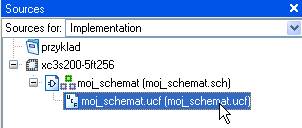

Dodać do projektu nowy plik ograniczeń użytkownika User Constraint File UCF:

wybierając typ pliku

Implementation Constraints File:

Dokonać

edycji nowego pliku UCF, wprowadzając informacje dot. podłączenia portów

projektowanego układu do konkretnych pinów układu scalonego FPGA:

Zaleca

się wklejenie informacji podanych na stronie WWW danego ćwiczenia, należy tylko

poprawić nazwy portów układu tak, aby nazywały się tak samo jak w projektowanym

układzie.

Wykonać

syntezę, implementację i generację pliku bit za pomocą

polecenia Generate Programming File: