Symulacja funkcjonalna projektu

Poniższy opis wykonano dla układu opisanego schematem

"moj_schemat.sch". Dla układów opisanych w języku HDL procedura jest

taka sama.

Najpierw

należy utworzyć plik z pobudzeniami dla testowanego układu. Można to zrobić na dwa

sposoby:

Sposób nr 1) (ZALECANY)

Pisząc testbench w języku VHDL lub Verilog – po prostu tworzymy nowy

moduł/entity w języku HDL (bez portów – są nie potrzebne), nazywamy go

np. testbench, a następnie osadzamy w nim symulowany układ. W pliku testbench

za pomocą języka HDL generujemy także sygnały pobudzające.

Sposób nr 2) Korzystając z

narzędzia Test Bench Waveform:

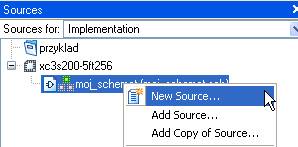

Dodajemy nowy plik do projektu:

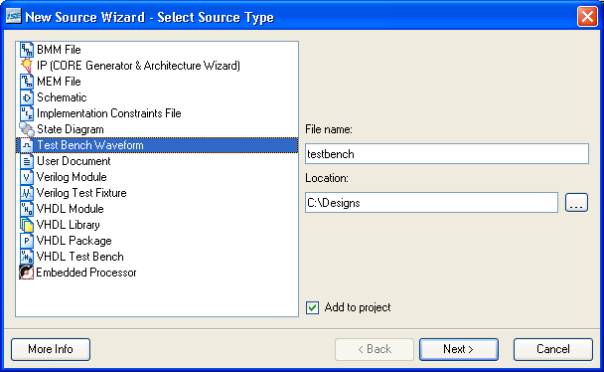

Wybieramy typ pliku Test Bench Waveform i wprowadzamy nazwę:

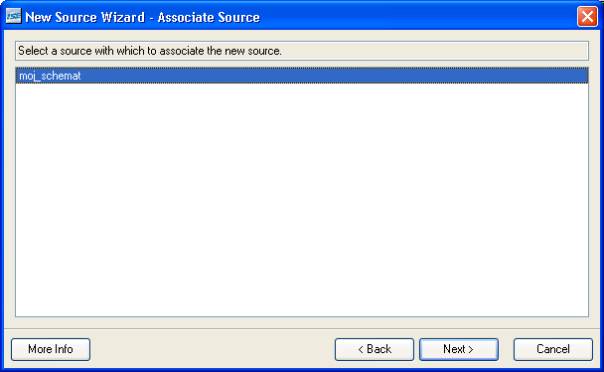

Następnie wybieramy plik, który ma być symulowany przez nasz nowy testbench:

i naciskamy Finish.

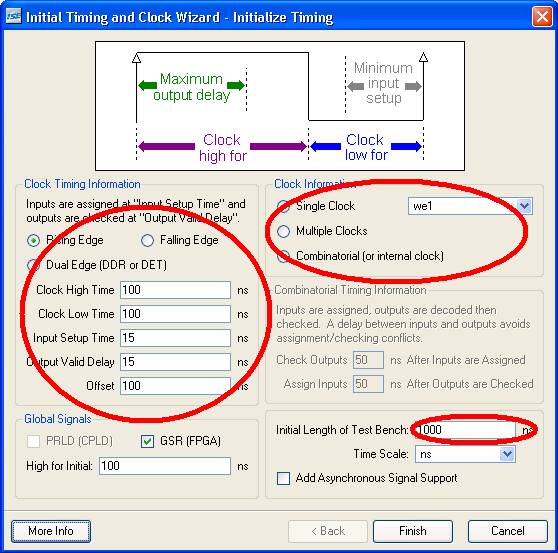

Wprowadzamy dane dot. pobudzeń:

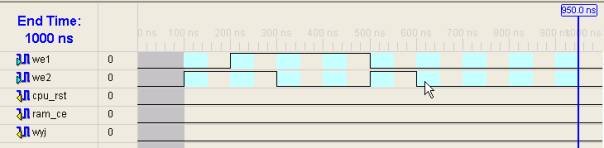

oraz w edytorze graficznym rysujemy przebiegi:

Na koniec należy zapisać plik oraz zamknąć okno graficzne testbencha.

UWAGA: Zaleca się korzystać ze sposobu nr 1.

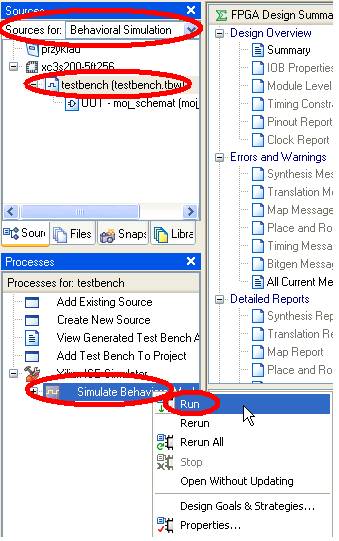

Po

lewej stronie ekranu zaznaczamy Sources for: Behavioral Simulation,

wybieramy plik, który będziemy symulować (czyli nasz testbench) i w

oknie Processes uruchamiamy symulację Simulate Behavioral Model:

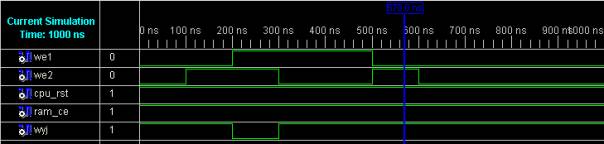

Utworzony

zostanie model do symulacji oraz otworzy się okno symulatora:

Przyciski

![]() służą do kontroli symulacji.

służą do kontroli symulacji.

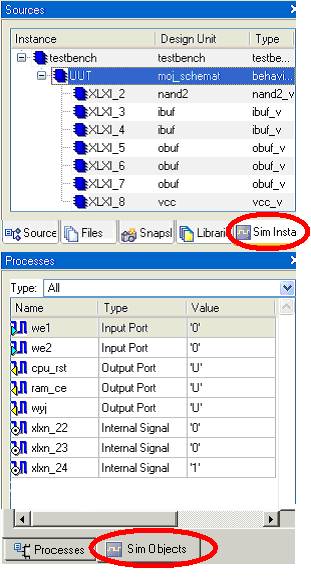

Z

okna po lewej stronie można dodawać dowolne sygnały i porty symulowanego układu

(upewnić się, że wybrano zakładki Sim Instances i Sim Objects).

Po dodaniu nowego sygnału, należy restartować symulację i uruchomić ją

ponownie, żeby nowy przebieg był widoczny.