Symulacja funkcjonalna projektu

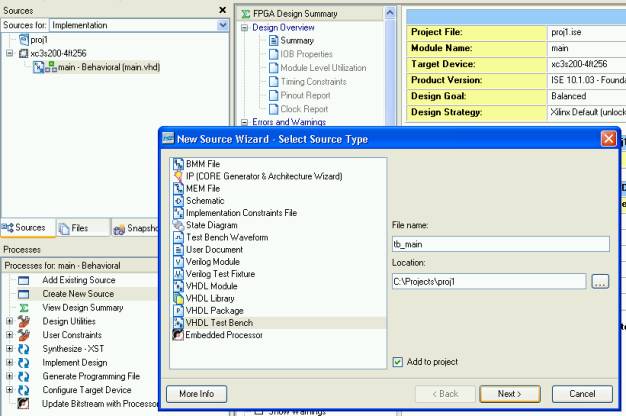

W okienku „Sources”

zaznaczmy plik będący modułem przeznaczonym do testowania. Następnie kliknijmy

w pole „Create New Source” w okienku „Processes”. Otworzy się okienko „New

Source Wizard” – „Select Source Type” w którym należy wybrać „VHDL Test Bench”

oraz wpisać nazwę pliku (zwyczajowo dopisujemy tb_ do nazwy modułu

testowanego):

Następnie należy kliknąć

„Next”.

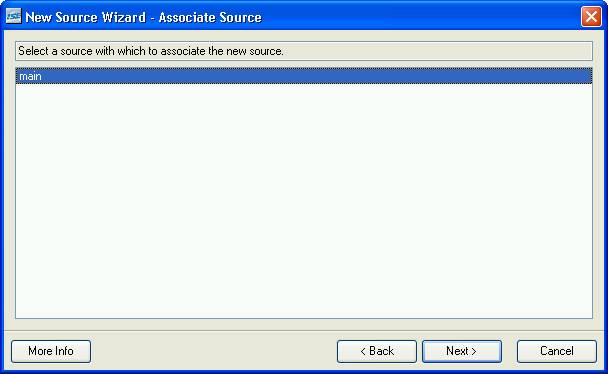

Następnie należy potwierdzić

wybór modułu który będzie testowany klikając „Next”.

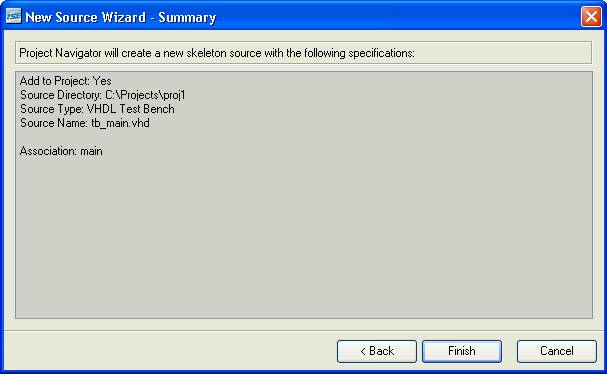

Teraz można kliknąć

„Finish”.

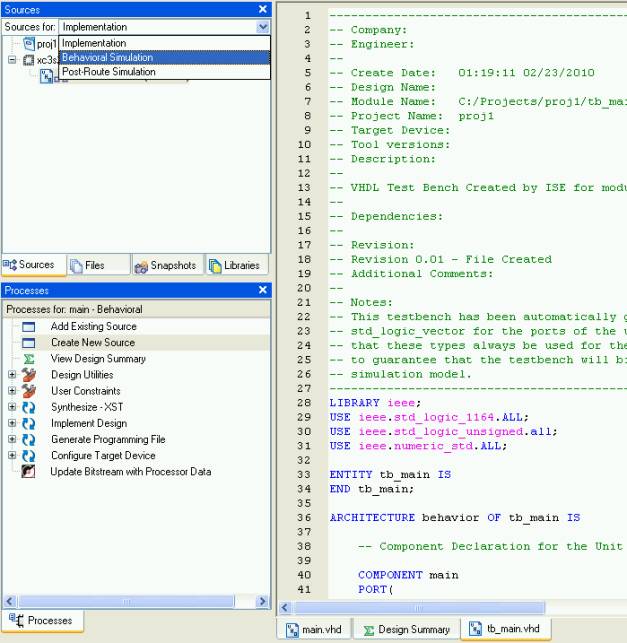

Po prawej stronie otwiera

się wygenerowany automatycznie szkielet testbencha z podłączonym modułem do

testowania (UUT).

Teraz musimy dopisać w nim

odpowiednie pobudzenia i możemy rozpocząć symulację.

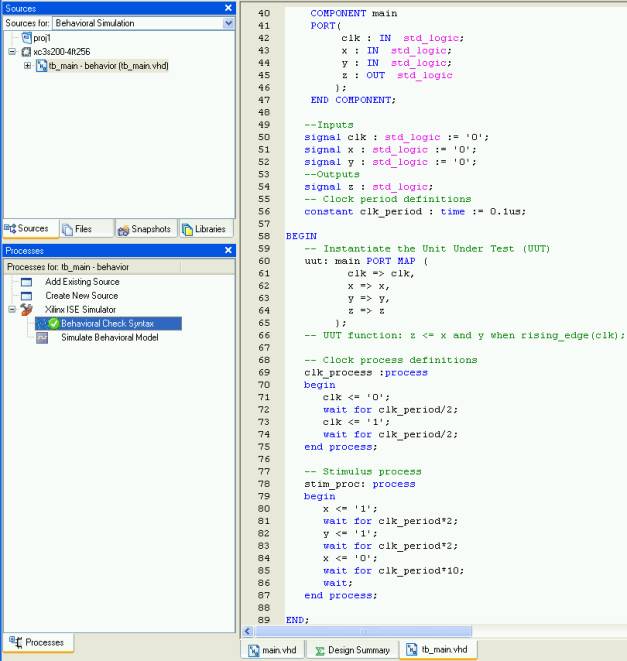

W okienku Sources

przełączamy na „Behavioral Simulation”:

Następnie w okienku

„Sources” zaznaczamy pole z nazwą pliku testbencha, a w okienku „Processes”

rozwijamy „Xilinx ISE Simulator” i klikamy w „Behavioral Check Syntax” w celu

sprawdzenia poprawności plików.

Potem możemy kliknąć w uruchamiające

symulację pole „Simulate Behavioral Model”.

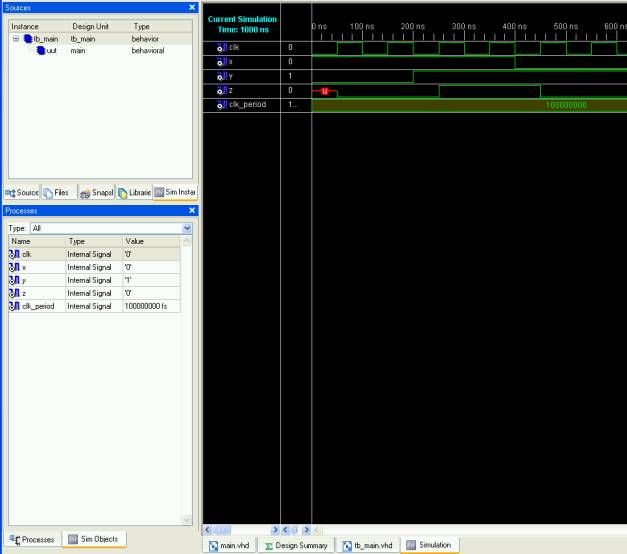

A oto rezultat symulacji:

Na symulację możemy wpływać

za pomocą ikonek:

![]()

Wybierając w okienku

„Sources” (zakładka „Sim Instances”) pliki należące do symulowanego projektu, a

następnie w okienku „Processes” (zakładka „Sim Objects”) sygnały znajdujące się

w tych plikach – można dopisywać nowe sygnały do wykresu czasowego symulacji.

Należy pamiętać o tym aby po dopisaniu nowych sygnałów zrestartować symulację

za pomocą ikonki: ![]()

Wtedy przebiegi nowych

sygnałów zostaną wyświetlone.