Inżynieria układów i

systemów scalonych

Laboratorium

Ćwiczenie 2

Wykonanie projektu

topografii wzmacniacza operacyjnego CMOS

1. Wstęp

Ćwiczenie ma na celu naukę wykonywania poprawnego projektu topografii. W niniejszym ćwiczeniu wykorzystywana jest technologia CMOS nwell 0.5um Amis C5.

2. Przygotowanie do laboratorium

Przed przystąpieniem do wykonania ćwiczenia należy odświeżyć wiadomości dotyczące budowy i działania wzmacniaczy operacyjnych, technik prawidłowego projektowania topografii układów jak również należy zapoznać się z obsługą edytora topografii MAGIC. Na końcu niniejszego opracowania podana jest niezbędna literatura.

3. Wzmacniacz operacyjny CMOS

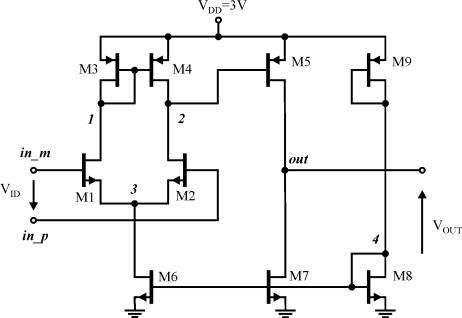

Schemat badanego wzmacniacza przedstawiony jest na rys. 1 i jest to ten sam wzmacniacz jak w ćwiczeniu nr 1. W tabeli poniżej umieszczone są wymagane rozmiary tranzystorów MOS wzmacniacza.

|

Element |

Typ |

Szerokość [mm] |

Długość [mm] |

|

M1 |

N |

24 |

1.5 |

|

M2 |

N |

24 |

1.5 |

|

M3 |

P |

5.4 |

1.5 |

|

M4 |

P |

5.4 |

1.5 |

|

M5 |

P |

20 x 5.4 |

1.5 |

|

M6 |

N |

5.4 |

1.5 |

|

M7 |

N |

10 x 5.4 |

1.5 |

|

M8 |

N |

5.4 |

1.5 |

|

M9 |

P |

1.2 |

1.5 |

|

Cc |

poly-poly |

0.5pF |

|

Rys. 1. Schemat badanego, prostego wzmacniacza operacyjnego CMOS. Kursywą podane są wymagane nazwy węzłów.

4. Zadania do wykonania

W ramach ćwiczenia należy wykonać projekt topografii wzmacniacza operacyjnego z rys. 1. Topografia ta ma być zaprojektowana z uwzględnieniem następujących wymagań:

A) Końcowy kształt topografii wzmacniacza powinien być w przybliżeniu kwadratem, maksymalna dysproporcja wymiarów 4:6.

B) Wejścia i wyjście powinny być po przeciwnych stronach i powinny być wyprowadzone na warstwie metalu 1.

C) Wyspy nwell powinny być otoczone pierścieniami ochronnymi.

D) Cały wzmacniacz też powinien być otoczony pierścieniem ochronnym.

E) Należy unikać stosowania warstw powyżej metalu 1.

F) Niektóre elementy (te dla których jest to w przypadku niniejszego wzmacniacza istotne) powinny być zaprojektowane z użyciem topografii common-centroid.

G) Szerokie tranzystory należy zaprojektować jako równoległe połączenie mniejszych.

H) Należy również zastosować odpowiednią liczbę kontaktów do podłoża i wyspy.

5. Literatura

[1] Z. Staszak., J. Glinianowicz, D. Czarnecki, skrypt pt. „Układy elektroniczne liniowe”.

[2] A. Guziński, „Liniowe elektroniczne układy analogowe”, WNT 1992.

[3] Strona domowa programu MAGIC http://opencircuitdesign.com/magic/index.html.

[4] Strona domowa firmy MOSIS - dystrybutora technologii Amis C5 http://www.mosis.com/

[4] B. Pankiewicz, materiały pomocnicze do przedmiotu „Inżynieria układów i systemów scalonych”, Gdańsk 2009.

6. Dodatki:

A) Tabela – wzór protokołu.

|

Ćwiczenie 2 - laboratorium

IUSS Wykonanie projektu

topografii wzmacniacza operacyjnego CMOS |

||

|

L.p. |

Nazwa / opis |

Wartość |

|

1 |

Data wykonania |

|

|

2 |

Osoby które wykonały ćwiczenie |

|

|

3 |

Wymiary zaprojektowanego wzmacniacza |

|

|

4 |

Rysunek topografii - wstawiony poniżej |

|

|

|

||

|

5 |

Wnioski końcowe: |

|

Ćwiczenie opracował Bogdan

Pankiewicz, Gdańsk, październik 2009