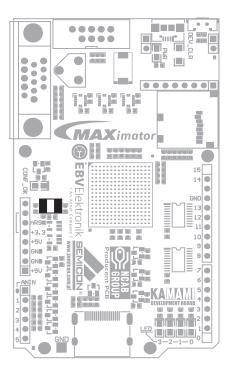

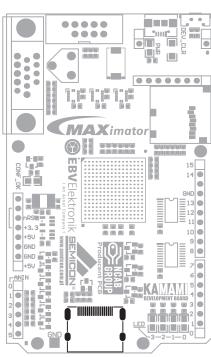

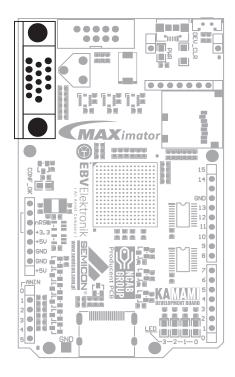

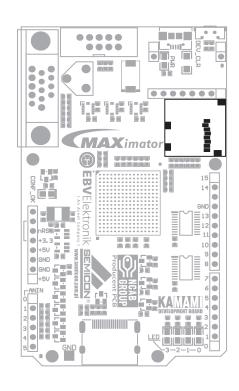

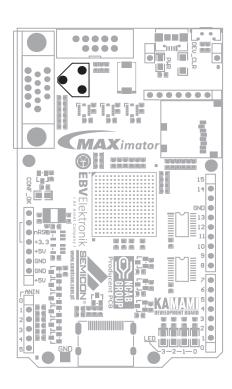

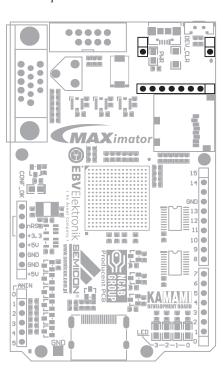

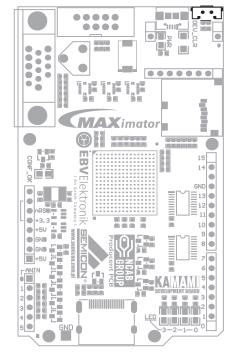

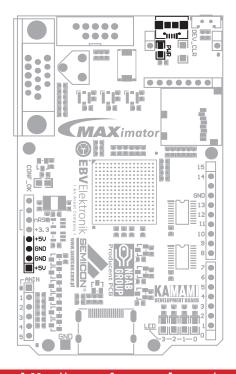

# **MAXimator**

# **Altera MAX10 FPGA Evaluation Board**

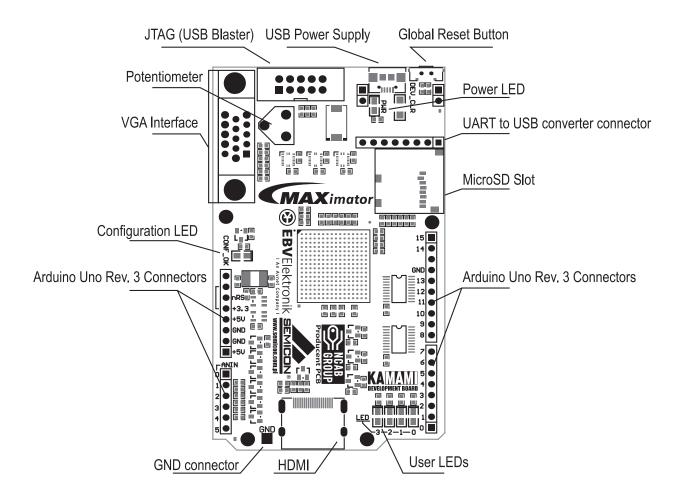

The MAXimator is an entry-level evaluation board with modern Altera MAX10 FPGA. The board can interface to external peripheral modules via Arduino Uno Rev 3 connectors. It also features HDMI+CEC+DCC and VGA interfaces

Board was developed by Kamami Labs in cooperation with:

ver. 1.0

#### **Features**

- ▶ Altera MAX10 FPGA, 10M08DAF256C8GES

- 8000 logic elements (LE)

- 378kb M9K embedded memory

- 1376kb (172kB) user Flash memory

- Built-in configuration Flash memory

- Built-in clocking circuit

- Analog-to-digital (ADC) converter, 1 million samples per second (MSPS), 12-bit

- 24 embedded multiplier blocks

- 2 built-in PLLs (Phase-locked loops)

- On-chip temperature sensor

- LVDS interfaces

- Arduino Uno Rev 3 connectors (5V)

- ▶ 5 ADC channels (12-bit, 1MSPS), overvoltage protection (Input voltage 0...+2.5V)

- ► HDMI interface (CEC, DDC)

- VGA video interface

- ▶ 10MHz crystal external generator

- ▶ 4 user LEDs

- ▶ Power LED, configuration LED

- Analog potentiometer

- ▶ MicroSD memory card slot

- UART to USB converter connector

- ▶ Altera Enpirion PowerSoC regulators

- ▶ Global reset button

- ▶ Powered from USB cable (protected by polymer fuse) or external 5V source

- ▶ JTAG header for external USB-Blaster download cable

Note! Please notice that Altera prepared errata sheet for 10M08DAF256C8GES (ES-1040). Please read this article as MAX10 engineering sample (ES) devices are not intended to be used for volume production or device qualification testing.

#### **Contents of the package**

| Code      | Description                   |

|-----------|-------------------------------|

| MAXimator | ▶ MAX10 FPGA Evaluation Board |

#### **Technical assistance**

For technical assistance, please contact support@kamami.com.

Please provide the following data:

- Version of the operating system

- Microcontroller type used in your system and its oscillator frequency

- ▶ Detailed description of the problem

#### Disclaimer

BTC Korporacja makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

BTC Korporacja products are not intended for use in medical, life saving or life sustaining applications.

BTC Korporacja retains the right to make changes to these specifications at any time, without notice.

All product names referenced herein are trademarks of their respective companies.

# **Board Components**

#### **Schematics**

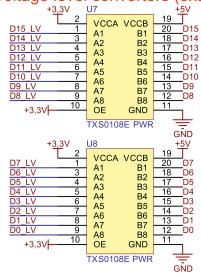

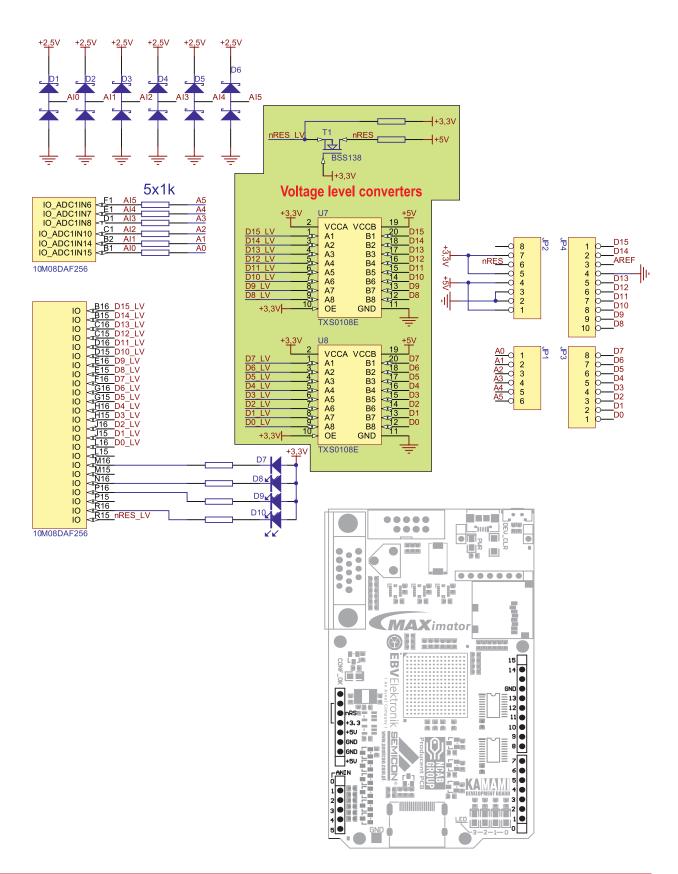

#### HiSpeed voltage level converters (external 5V logic)

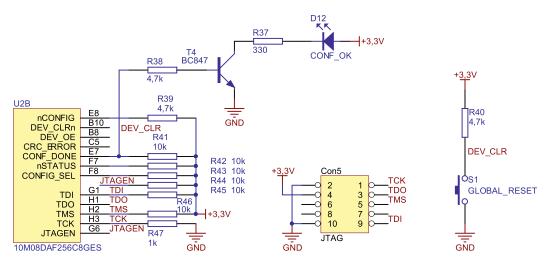

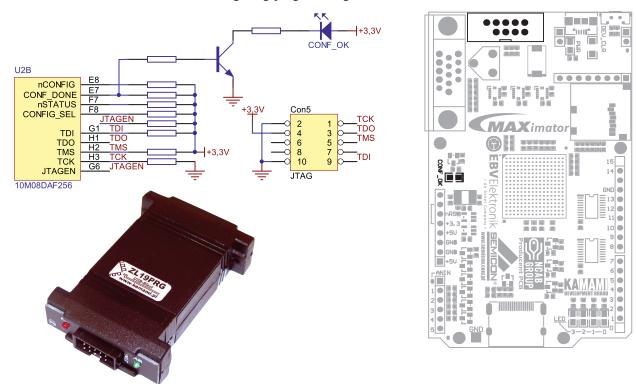

JTAG connector + configuration signalling + nGRES

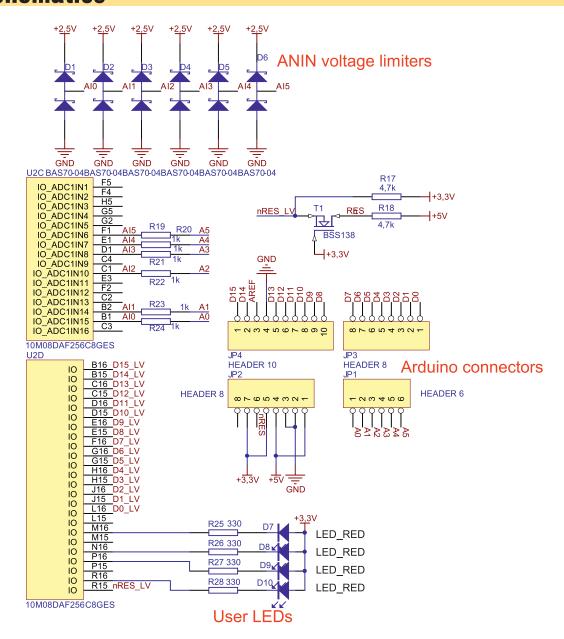

#### **Arduino Connectors**

All digital inputs/outputs are connected to FPGA via bidirectional voltage-level translators 3.3/5V.

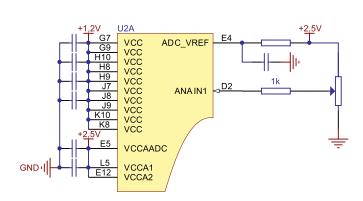

Analog inputs Ax support voltages from 0V to 2.5V which is the maximum allowable voltage per the MAX 10 FPGA integrated analog-to-digital converter.

Ax lines may work as a digital lines (GPIO) – please notice that there are  $1k\Omega$  resistors connected in series.

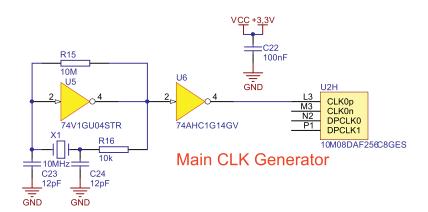

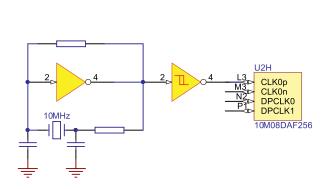

#### **Clock Circuit**

The external clock source for the FPGA is the 10MHz oscillator. The signal is provided to the FPGA global clock input CLK0p.

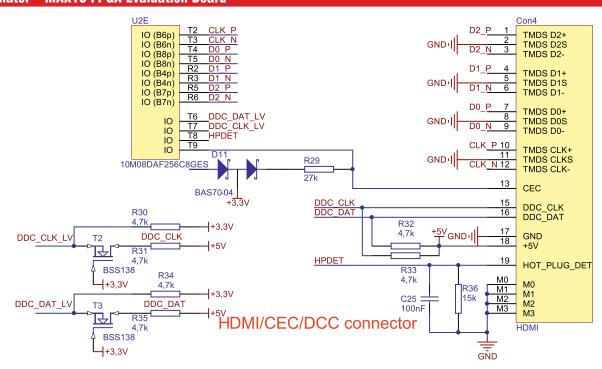

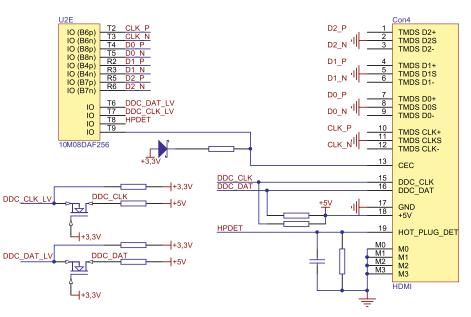

#### **HDMI/CEC/DDC Interface**

The MAXimator board contains one HDMI connector. It allows you to connect a monitor and use the Consumer Electronics Control (CEC) bus and the Display Data Channel (DDC) bus.

Note! To use HDMI/CEC/DDC interface you need the proper IP Core implemented in FPGA.

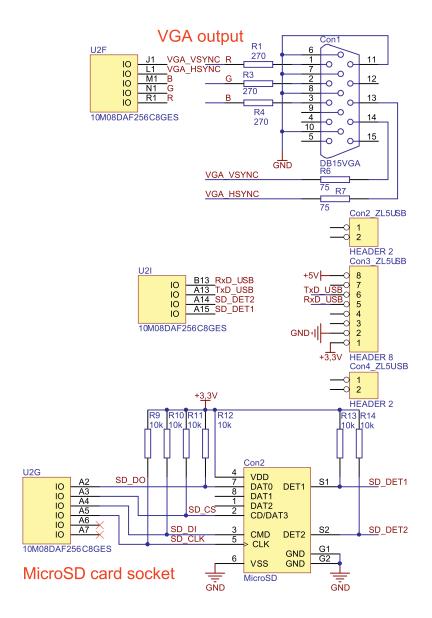

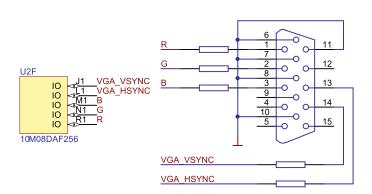

#### **VGA Interface**

The MAXimator board contains one VGA connector which allows you to display a 8-colour image with an analog monitor.

Note! To use VGA interface you need the proper IP Core implemented in FPGA.

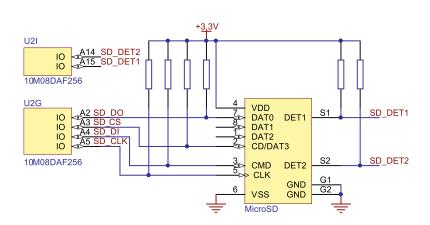

#### **MicroSD Slot**

The MicroSD memory card is supported by FPGA in 1-bit mode. The interface works with TTL-LV 3.3V. *Note! To use microSD memory cards you need the proper IP Core implemented in FPGA.*

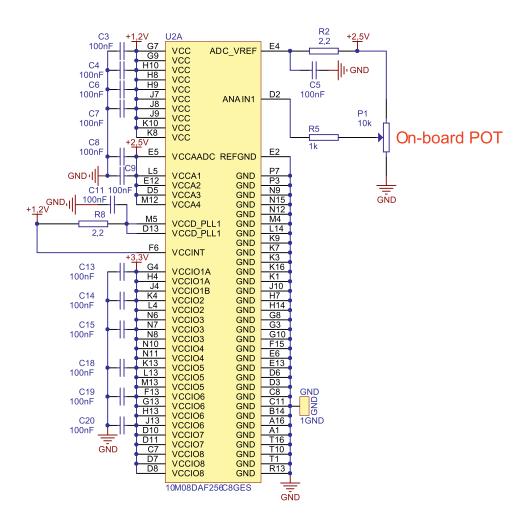

### **Analog Potentiometer**

The MAXimator board contains one analog potentiometer connected to analog input ANAIN1 of MAX10 FPGA ADC. It allows you to adjust voltage from 0V to 2.5V.

Note! To use ADC you need the proper IP Core implemented in FPGA

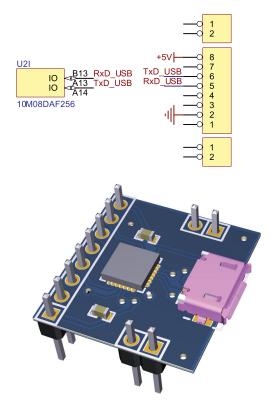

#### **UART to USB converter connector**

The MAXimator board can be equipped with the bidirectional UART to USB converter (eg. ZL5USB module shown in the picture below).

Note! To use UART to USB converter you need the proper IP Core implemented in FPGA.

#### **JTAG Connector**

The MAXimator board contains a JTAG connector for configuring/programming the FPGA using an external Altera USB-Blaster (or compatible) download cable.

The JTAG connector can be used for programming configuration flash memory of MAX10 FPGA or for configuration by downloading a file to the FPGA SRAM memory.

The JTAG connector can be also used for the SignalTap logic analyzer.

The CONF\_OK LED is on when configuring/programming the MAX10 FPGA is successful.

ZL19PRG USB-Byte Blaster – compatible download cable (optional programmer, compatible with USB Blaster)

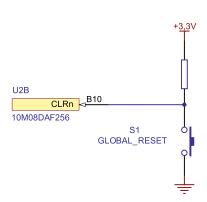

#### **Global Reset Button**

The MAXimator board contains a global reset button which resets all flip-flops in the MAX10 FPGA if device-wide reset is enabled in Quartus Prime tool.

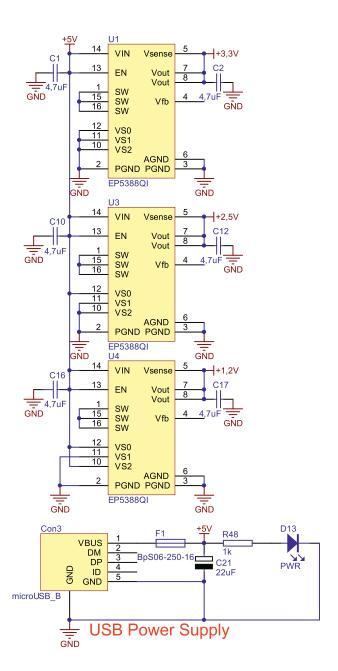

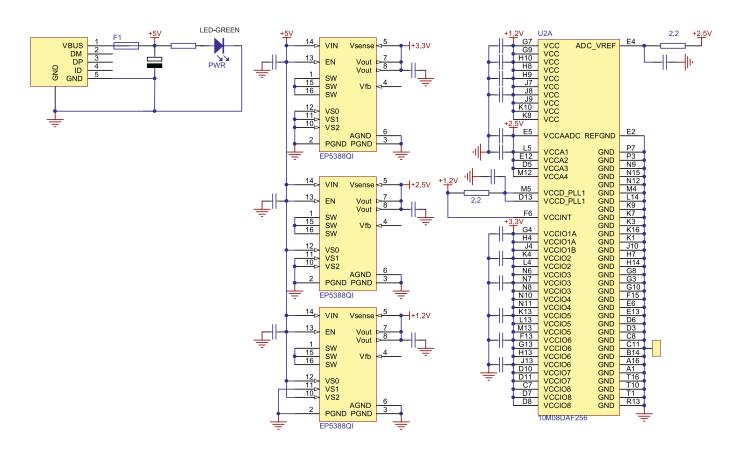

## **Power Supply**

The MAXimator board contains modern Enpirion PowerSoC regulators. Voltage regulator circuits generate the voltages required by the FPGA and peripherals:

- +1.2V power supply for PLL and FPGA core

- +2.5V power supply for analog circuits of FPGA

- +3.3V power supply for I/O lines

The board is powered by USB cable (from PC or wall jack) connected to microUSB connector or to the UART to USB converter (ZL5USB) or by an external power supply (+5V and GND connected to pin header JP2).

#### **Notes**

- 1. All GPIO lines are bidirectional (3.3V, 5V).

- 2. The maximum voltage for analog inputs ANIN of the MAX 10 FPGA ADC is from 0V to 2.5 V.

- 3. The ADC1\_8 line (ANIN3) is equipped with programmable voltage divider 1:2.

- 4. The MicroSD memory card interface works with 3.3V.

- 5. The nRES line works with 3.3V and 5V.