# **Constraints Guide**

10.1

Xilinx is disclosing this user guide, manual, release note, and/or specification (the "Documentation") to you solely for use in the development of designs to operate with Xilinx hardware devices. You may not reproduce, distribute, republish, download, display, post, or transmit the Documentation in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Xilinx expressly disclaims any liability arising out of your use of the Documentation. Xilinx reserves the right, at its sole discretion, to change the Documentation without notice at any time. Xilinx assumes no obligation to correct any errors contained in the Documentation, or to advise you of any corrections or updates. Xilinx expressly disclaims any liability in connection with technical support or assistance that may be provided to you in connection with the Information.

THE DOCUMENTATION IS DISCLOSED TO YOU "AS-IS" WITH NO WARRANTY OF ANY KIND. XILINX MAKES NO OTHER WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE DOCUMENTATION, INCLUDING ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NONINFRINGEMENT OF THIRD-PARTY RIGHTS. IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL DAMAGES, INCLUDING ANY LOSS OF DATA OR LOST PROFITS, ARISING FROM YOUR USE OF THE DOCUMENTATION.

© 2002-2008 Xilinx, Inc. All rights reserved.

XILINX, the Xilinx logo, the Brand Window, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.

# About This Guide

The Xilinx® *Constraints Guide* describes constraints and attributes that can be attached to designs for Xilinx FPGA and CPLD devices. This chapter contains the following sections:

- "Guide Contents"

- "Additional Resources"

- "Conventions"

#### **Guide Contents**

This Guide contains the following chapters:

- Chapter 1, "Introduction," discusses What's New in this Guide for ISE™ Release 10.1, and provides a Supported Architectures table showing the Xilinx devices supported for each constraint.

- Chapter 2, "Constraint Types," discusses the various types of constraints documented within this Guide, including CPLD fitter, grouping constraints, logical constraints, physical constraints, mapping directives, placement constraints, placement constraints, routing directives, synthesis constraints, timing constraints

- Chapter 3, "Entry Strategies for Xilinx Constraints," discusses entry strategies for Xilinx constraints, including which feature of the ISE software to use to enter a given constraint type.

- Chapter 4, "Timing Constraint Strategies," provides general guidelines that explain how to constrain the timing on designs when using the implementation tools for FPGA devices.

- Chapter 5, "Xilinx Constraints," describes the individual constraints that can be used with Xilinx FPGA and CPLD devices, including, for each constraint, architecture support, applicable elements, description, propagation rules, syntax examples, and, where necessary, additional information for particular constraints.

### **Additional Resources**

To find additional documentation, see the Xilinx website at:

http://www.xilinx.com/literature.

To search the Answer Database of silicon, software, and IP questions and answers, or to create a technical support WebCase, see the Xilinx website at:

http://www.xilinx.com/support.

# **Conventions**

This document uses the following conventions. An example illustrates each convention.

# Typographical

The following typographical conventions are used in this document:

| Convention          | Meaning or Use                                                                                               | Example                                                                                            |

|---------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Courier font        | Messages, prompts, and program files that the system displays                                                | speed grade: - 100                                                                                 |

| Courier bold        | Literal commands that you enter in a syntactical statement                                                   | ngdbuild design_name                                                                               |

| Helvetica bold      | Commands that you select from a menu                                                                         | File →Open                                                                                         |

|                     | Keyboard shortcuts                                                                                           | Ctrl+C                                                                                             |

|                     | Variables in a syntax<br>statement for which you must<br>supply values                                       | ngdbuild design_name                                                                               |

| Italic font         | References to other manuals                                                                                  | See the <i>Development System Reference Guide</i> for more information.                            |

|                     | Emphasis in text                                                                                             | If a wire is drawn so that it overlaps the pin of a symbol, the two nets are <i>not</i> connected. |

| Square brackets []  | An optional entry or parameter. However, in bus specifications, such as <b>bus</b> [7:0], they are required. | ngdbuild [option_name] design_name                                                                 |

| Braces { }          | A list of items from which you must choose one or more                                                       | lowpwr ={on off}                                                                                   |

| Vertical bar        | Separates items in a list of choices                                                                         | lowpwr ={on off}                                                                                   |

| Vertical ellipsis   | Repetitive material that has been omitted                                                                    | IOB #1: Name = QOUT' IOB #2: Name = CLKIN'                                                         |

| Horizontal ellipsis | Repetitive material that has been omitted                                                                    | allow block block_name loc1 loc2 locn;                                                             |

### **Online Document**

The following conventions are used in this document:

| Convention            | Meaning or Use                                             | Example                                                                                                         |

|-----------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| Blue text             | Cross-reference link to a location in the current document | See the section "Additional<br>Resources" for details.<br>Refer to "Title Formats" in<br>Chapter 1 for details. |

| Red text              | Cross-reference link to a location in another document     | See Figure 2-5 in the <i>Virtex</i> <sup>TM</sup> - <i>II Handbook</i> .                                        |

| Blue, underlined text | Hyperlink to a website (URL)                               | Go to <a href="http://www.xilinx.com">http://www.xilinx.com</a> for the latest speed files.                     |

# Table of Contents

| Preface: About This Guide                          |

|----------------------------------------------------|

| Guide Contents                                     |

| Additional Resources                               |

| Conventions                                        |

| Chapter 1: Introduction                            |

| <b>What's New</b>                                  |

| Supported Architectures                            |

| Chapter 2: Constraint Types                        |

| Attributes and Constraints                         |

| <b>CPLD Fitter</b>                                 |

| Grouping Constraints 1                             |

| Logical Constraints2                               |

| Physical Constraints                               |

| Mapping Directives 2                               |

| Placement Constraints                              |

| Routing Directives                                 |

| Synthesis Constraints                              |

| Timing Constraints 2                               |

| Configuration Constraints                          |

| Chapter 3: Entry Strategies for Xilinx Constraints |

| Constraints Entry Methods                          |

| Constraints Entry Table                            |

| Schematic Design 3                                 |

| VHDL 3                                             |

| <b>Verilog</b>                                     |

| <b>ABEL</b> 3                                      |

| UCF                                                |

| UCF and NCF File Syntax 3                          |

| PCF4                                               |

| NCF 4                                              |

| Constraints Editor 4                               |

| UCF Syntax 4                                       |

| Project Navigator5                                 |

| Floorplanner 5                                     |

| Floorplan Editor5                                  |

| PACE                                                                                                           | 51              |

|----------------------------------------------------------------------------------------------------------------|-----------------|

| Partial Design Pin Preassignment                                                                               | 52              |

| FPGA Editor                                                                                                    | 53              |

| Constraints Priority                                                                                           | 55              |

|                                                                                                                |                 |

| Chapter 4: Timing Constraint Strategies                                                                        |                 |

| Basic Implementation Tools Constraining Methodology                                                            | 57              |

| Global Timing Assignments                                                                                      | 58              |

| Specific Timing Assignments                                                                                    | 61              |

| Multi-Cycle and Fast or Slow Timing Assignments                                                                | 63              |

| Specific OFFSET Constraints Using PAD and or Register Groups                                                   |                 |

| Special Case Path Constraining                                                                                 | 67              |

| Path Coverage Statistics                                                                                       | 69              |

| Static Timing Analysis                                                                                         | 70              |

| Synchronous Timing                                                                                             | 72              |

| Directed Routing                                                                                               | 74              |

| , and the second se |                 |

| Chapter 5: Xilinx Constraints                                                                                  |                 |

| Constraint Information                                                                                         | 77              |

| Alphabetized List of Xilinx Constraints                                                                        | 78              |

| Area Group (AREA_GROUP)                                                                                        | 81              |

| Asynchronous Register (ASYNC_REG)                                                                              | 87              |

| BEL                                                                                                            | 89              |

| Block Name (BLKNM)                                                                                             | 91              |

| BUFG (CPLD)                                                                                                    | 93              |

| Clock Dedicated Route                                                                                          | 95              |

| Collapse (COLLAPSE)                                                                                            | 97              |

| Component Group (COMPGRP)                                                                                      | 99              |

| CoolCLOCK (COOL_CLK)                                                                                           | 100             |

| Configuration                                                                                                  | <b>)E)</b> 102  |

| Data                                                                                                           |                 |

| DCI_CASCADE                                                                                                    | 106             |

| DCI_VALUE                                                                                                      | 109             |

| Directed Routing (DIRECTED_ROUTING)                                                                            | 110             |

| Disable (DISABLE)                                                                                              | 112             |

| Drive (DRIV                                                                                                    | / <b>E)</b> 114 |

| Drop Specifications (DROP_SPEC)                                                                                | 117             |

| Enable (ENABLE)                                                                                                |                 |

| Enable Suspend (ENABLE_SUSPEND)                                                                                |                 |

| Fast (FAST)                                                                                                    |                 |

| Feedback (FEEDBACK)                                                                                            |                 |

| File (FILE)                                                                                                    |                 |

| Float (FLOAT)                                                                                                  | 127             |

| From Thru T o (FROM-THRU-TO) 12             |    |

|---------------------------------------------|----|

| From To (FROM-TO)                           | 31 |

| Hierarchical Block Name (HBLKNM)            | 33 |

| Hierarchical Lookup Table Name (HLUTNM)     | 36 |

| HU_SET                                      | 39 |

| Input Buffer Delay Value (IBUF_DELAY_VALUE) | 41 |

| IFD_DELAY_VALUE                             | 13 |

| Input Registers (INREG)                     | 45 |

| IOB                                         | 16 |

| Input Output Block Delay (IOBDELAY)         | 18 |

| Input Output Standard (IOSTANDARD)          | 50 |

| Keep (KEEP)                                 | 53 |

| <b>Keeper (KEEPER)</b>                      | 55 |

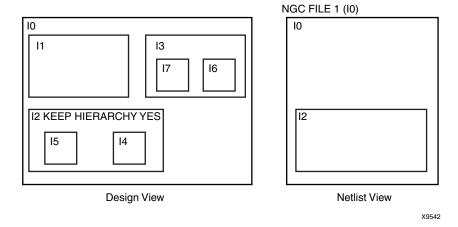

| Keep Hierarchy (KEEP_HIERARCHY)             | 57 |

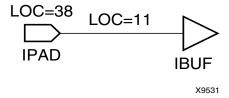

| <b>Location (LOC)</b>                       | 50 |

| <b>Locate (LOCATE)</b>                      | 37 |

| <b>Lock Pins (LOCK_PINS)</b>                | 39 |

| Lookup Table Name (LUTNM)                   | 91 |

| <b>Map (MAP)</b>                            | 94 |

| Maximum Delay (MAXDELAY)                    | 96 |

| Maximum Product Terms (MAXPT)               | 98 |

| Maximum Skew (MAXSKEW)                      | 00 |

| <b>No Delay (NODELAY)</b>                   | )2 |

| No Reduce (NOREDUCE)                        | )4 |

| Offset In (OFFSET IN)                       | )6 |

| Offset Out (OFFSET OUT)                     | 12 |

| Open Drain (OPEN_DRAIN)                     | 17 |

| Optimizer Effort (OPT_EFFORT)               | 19 |

| <b>Optimize (OPTIMIZE)</b>                  | 20 |

| <b>Period (PERIOD)</b>                      | 22 |

| <b>Pin (PIN)</b>                            | 31 |

| <b>POST_CRC</b> 23                          | 32 |

| POST_CRC_ACTION                             | 34 |

| POST_CRC_FREQ                               | 36 |

| POST_CRC_SIGNAL 23                          | 37 |

| <b>Priority (PRIORITY)</b>                  | 39 |

| <b>Prohibit (PROHIBIT)</b>                  | 40 |

| Pulldown (PULLDOWN)24                       | 14 |

| <b>Pullup (PULLUP)</b>                      | 46 |

| Power Mode (PWR_MODE)                       | 18 |

| <b>Registers (REG)</b>                      | 50 |

| Relative Location (RLOC)                    |    |

| Relative Location Origin (RLOC_ORIGIN)      | 32 |

| Relative Location Range (RLOC_RANGE)           | 284 |

|------------------------------------------------|-----|

| Save Net Flag (SAVE NET FLAG)                  | 287 |

| Schmitt Trigger (SCHMITT_TRIGGER)              | 289 |

| Slew (SLEW)                                    | 291 |

| Slow (SLOW)                                    | 293 |

| Stepping (STEPPING)                            | 295 |

| Suspend (SUSPEND)                              | 296 |

| System Jitter (SYSTEM_JITTER)                  | 298 |

| Temperature (TEMPERATURE)                      | 300 |

| Timing Ignore (TIG)                            | 302 |

| Timing Group (TIMEGRP)                         | 306 |

| Timing Specifications (TIMESPEC)               | 311 |

| Timing Name (TNM)                              | 314 |

| Timing Name Net (TNM_NET)                      | 322 |

| Timing Point Synchronization (TPSYNC)          | 326 |

| Timing Thru Points (TPTHRU)                    | 329 |

| Timing Specification Identifier (TSidentifier) | 332 |

| U_SET                                          | 336 |

| Use Relative Location (USE_RLOC)               | 338 |

| Use Low Skew Lines (USELOWSKEWLINES)           | 340 |

| VCCAUX                                         | 342 |

| Voltage (VOLTAGE)                              | 343 |

| VREF                                           | 345 |

| Wire And (WIREAND)                             | 347 |

| XBLKNM                                         | 349 |

# Introduction

This chapter discusses What's New in this Guide for ISE<sup>TM</sup> Release 9.1i, and provides a Supported Architectures table showing the Xilinx<sup>®</sup> devices supported for each constraint. This chapter contains the following sections:

- "What's New"

- "Supported Architectures"

#### What's New

The following changes have been made to this edition (ISE Release 9.1i) of the Xilinx *Constraints Guide*.

- "DCI\_CASCADE" constraint added (Virtex<sup>TM</sup>-5)

- "Hierarchical Lookup Table Name (HLUTNM)" constraint added (Virtex-5)

- "Enable Suspend (ENABLE\_SUSPEND)" constraint added (Spartan™-3A)

- "Stepping (STEPPING)" constraint added

- "Attributes and Constraints" and "Configuration Constraints" sections added to Chapter 2, "Constraint Types"

# **Supported Architectures**

The Supported Architectures table shows the Xilinx devices supported for each constraint. Contact Xilinx Technical Support if you need information for Xilinx architectures not shown.

Table 1-1: Supported Architectures

| Constraint                 |        |          |           |               |                 |          | Arc      | hitec      | ture        |           |            |            |              |                 |               |

|----------------------------|--------|----------|-----------|---------------|-----------------|----------|----------|------------|-------------|-----------|------------|------------|--------------|-----------------|---------------|

|                            | Virtex | Virtex-E | Virtex-II | Virtex-II Pro | Virtex-II Pro X | Virtex-4 | Virtex-5 | Spartan-II | Spartan-IIE | Spartan-3 | Spartan-3A | Spartan-3E | XC9500/XL\XV | CoolRunnerXPLA3 | CoolRunner-II |

| Constraints A              |        |          |           |               |                 |          |          |            |             |           |            |            |              |                 |               |

| Area Group<br>(AREA_GROUP) | Yes    | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | No           | No              | No            |

Table 1-1: Supported Architectures

| Constraint                          | Architecture |          |           |               |                 |          |          |            |             |           |            |            |              |                 |               |

|-------------------------------------|--------------|----------|-----------|---------------|-----------------|----------|----------|------------|-------------|-----------|------------|------------|--------------|-----------------|---------------|

|                                     | Virtex       | Virtex-E | Virtex-II | Virtex-II Pro | Virtex-II Pro X | Virtex-4 | Virtex-5 | Spartan-II | Spartan-IIE | Spartan-3 | Spartan-3A | Spartan-3E | XC9500\XL\XV | CoolRunnerXPLA3 | CoolRunner-II |

| Asynchronous Register (ASYNC_REG)   | Yes          | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | No           | No              | No            |

| Constraints B                       |              |          |           |               |                 |          |          |            |             |           |            |            |              |                 |               |

| BEL                                 | No           | No       | Yes       | Yes           | Yes             | Yes      | Yes      | No         | No          | Yes       | Yes        | Yes        | No           | No              | No            |

| Block Name (BLKNM)                  | Yes          | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | No           | No              | No            |

| BUFG (CPLD)                         | No           | No       | No        | No            | No              | No       | No       | No         | No          | No        | No         | No         | Yes          | Yes             | Yes           |

| Constraints C                       |              |          |           |               |                 |          |          |            |             |           |            |            |              |                 |               |

| Clock Dedicated Route               | No           | No       | No        | No            | No              | Yes      | Yes      | No         | No          | Yes       | Yes        | Yes        | No           | No              | No            |

| Collapse (COLLAPSE)                 | No           | No       | No        | No            | No              | No       | No       | No         | No          | No        | No         | No         | Yes          | Yes             | Yes           |

| Component Group<br>(COMPGRP)        | Yes          | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | No           | No              | No            |

| Configuration Mode<br>(CONFIG_MODE) | Yes          | Yes      | Yes       | Yes           | Yes             | Yes      | No       | Yes        | Yes         | Yes       | No         | No         | No           | No              | No            |

| CoolCLOCK (COOL_CLK)                | No           | No       | No        | No            | No              | No       | No       | No         | No          | No        | No         | No         | No           | No              | Yes           |

| Constraints D                       | •            |          |           |               |                 | •        |          | •          |             | •         |            |            | •            | I               |               |

| Data Gate (DATA_GATE)               | No           | No       | No        | No            | No              | No       | No       | No         | No          | No        | No         | No         | No           | No              | Yes           |

| DCI_CASCADE                         | No           | No       | No        | No            | No              | No       | Yes      | No         | No          | No        | No         | No         | No           | No              | No            |

| DCI_VALUE                           | No           | No       | Yes       | Yes           | Yes             | Yes      | Yes      | No         | No          | Yes       | No         | No         | No           | No              | No            |

| Directed Routing (DIRECTED_ROUTING) | No           | No       | Yes       | Yes           | No              | Yes      | Yes      | No         | No          | Yes       | Yes        | Yes        | No           | No              | No            |

| Disable (DISABLE)                   | Yes          | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | No           | No              | No            |

| D rive (DRIVE)                      | Yes          | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | No           | No              | No            |

| Drop Specifications<br>(DROP_SPEC)  | Yes          | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | Yes          | Yes             | Yes           |

| Constraints E                       |              | ,        |           |               |                 |          |          |            |             |           |            |            |              | ,               |               |

| Enable (ENABLE)                     | Yes          | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | No           | No              | No            |

| Enable Suspend<br>(ENABLE_SUSPEND)  | No           | No       | No        | No            | No              | No       | No       | No         | No          | No        | Yes        | No         | No           | No              | No            |

| Constraints F                       |              |          |           |               |                 |          |          |            |             |           |            |            |              |                 |               |

Table 1-1: Supported Architectures

| Constraint                                  | Architecture |          |           |               |                 |          |          |            |             |           |            |            |              |                 |               |

|---------------------------------------------|--------------|----------|-----------|---------------|-----------------|----------|----------|------------|-------------|-----------|------------|------------|--------------|-----------------|---------------|

|                                             | Virtex       | Virtex-E | Virtex-II | Virtex-II Pro | Virtex-II Pro X | Virtex-4 | Virtex-5 | Spartan-II | Spartan-IIE | Spartan-3 | Spartan-3A | Spartan-3E | XC9500/XL\XV | CoolRunnerXPLA3 | CoolRunner-II |

| Fast (FAST)                                 | Yes          | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | Yes          | Yes             | Yes           |

| Feedback (FEEDBACK)                         | Yes          | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | No           | No              | No            |

| File (FILE)                                 | Yes          | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | Yes          | Yes             | Yes           |

| Float (FLOAT)                               | No           | No       | No        | No            | No              | No       | No       | No         | No          | No        | No         | No         | No           | Yes             | Yes           |

| From Thru T o (FROM-THRU-TO)                | Yes          | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | No           | No              | No            |

| From To (FROM-TO)                           | Yes          | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | Yes          | Yes             | Yes           |

| Constraints H                               |              |          |           |               |                 |          |          |            |             |           |            |            |              |                 |               |

| Hierarchical Block Name<br>(HBLKNM)         | Yes          | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | No           | No              | No            |

| Hierarchical Lookup Table<br>Name (HLUTNM)  | No           | No       | No        | No            | No              | No       | Yes      | No         | No          | No        | No         | No         | No           | No              | No            |

| HU_SET                                      | Yes          | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | No           | No              | No            |

| Constraints I                               | <u>I</u>     | L.       |           |               | l I             | ı        |          | ı          |             | UI.       | l.         | 1          | ı            | l.              |               |

| Input Buffer Delay Value (IBUF_DELAY_VALUE) | No           | No       | No        | No            | No              | Yes      | Yes      | No         | No          | No        | Yes        | Yes        | No           | No              | No            |

| IFD_DELAY_VALUE                             | No           | No       | No        | No            | No              | Yes      | Yes      | No         | No          | No        | Yes        | Yes        | No           | No              | No            |

| Input Registers (INREG)                     | No           | No       | No        | No            | No              | No       | No       | No         | No          | No        | No         | No         | No           | Yes             | Yes           |

| IOB                                         | Yes          | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | No           | No              | No            |

| Input Output Block Delay (IOBDELAY)         | Yes          | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | No           | No              | No            |

| Input Output Standard (IOSTANDARD)          | Yes          | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | Yes          | No              | Yes           |

| Constraints K                               | I            |          |           |               | l I             |          |          |            |             | l.I       |            |            |              |                 |               |

| Keep (KEEP)                                 | Yes          | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | Yes          | Yes             | Yes           |

| Keeper (KEEPER)                             | Yes          | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | No           | No              | Yes           |

| Keep Hierarchy<br>(KEEP_HIERARCHY)          | Yes          | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | Yes          | Yes             | Yes           |

| Constraints L                               | ı            |          |           | 1             | ı I             | 1        | <u> </u> | 1          | I           | 11        | 1          | 1          | 1            | 1               |               |

| Location (LOC)                              | Yes          | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | Yes          | Yes             | Yes           |

Table 1-1: Supported Architectures

| Constraint                       | Architecture |          |           |               |                 |          |          |            |             |           |            |            |              |                 |               |

|----------------------------------|--------------|----------|-----------|---------------|-----------------|----------|----------|------------|-------------|-----------|------------|------------|--------------|-----------------|---------------|

|                                  | Virtex       | Virtex-E | Virtex-II | Virtex-II Pro | Virtex-II Pro X | Virtex-4 | Virtex-5 | Spartan-II | Spartan-IIE | Spartan-3 | Spartan-3A | Spartan-3E | XC9500\XL\XV | CoolRunnerXPLA3 | CoolRunner-II |

| Locate (LOCATE)                  | Yes          | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | No           | No              | No            |

| Lock Pins (LOCK_PINS)            | Yes          | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | No           | No              | No            |

| Lookup Table Name<br>(LUTNM)     | No           | No       | No        | No            | No              | No       | Yes      | No         | No          | No        | No         | No         | No           | No              | No            |

| Constraints M                    |              |          |           |               |                 |          |          |            |             |           |            |            |              |                 |               |

| Map (MAP)                        | Yes          | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | No           | No              | No            |

| Maximum Delay<br>(MAXDELAY)      | Yes          | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | No           | No              | No            |

| Maximum Product Terms (MAXPT)    | No           | No       | No        | No            | No              | No       | No       | No         | No          | No        | No         | No         | Yes          | Yes             | Yes           |

| Maximum Skew<br>(MAXSKEW)        | Yes          | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | No           | No              | No            |

| Constraints N                    | 11           |          |           |               |                 |          |          |            |             |           |            |            |              |                 |               |

| No Delay (NODELAY)               | Yes          | Yes      | Yes       | Yes           | Yes             | No       | No       | Yes        | Yes         | Yes       | Yes        | Yes        | No           | No              | No            |

| No Reduce (NOREDUCE)             | No           | No       | No        | No            | No              | No       | No       | No         | No          | No        | No         | No         | Yes          | Yes             | Yes           |

| Constraints O                    |              |          |           |               |                 |          |          |            |             |           |            |            |              |                 |               |

| Offset In (OFFSET IN)            | Yes          | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | Yes          | Yes             | Yes           |

| Offset Out (OFFSET OUT)          | Yes          | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | Yes          | Yes             | Yes           |

| Open Drain<br>(OPEN_DRAIN)       | No           | No       | No        | No            | No              | No       | No       | No         | No          | No        | No         | No         | No           | No              | Yes           |

| Optimizer Effort<br>(OPT_EFFORT) | Yes          | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | No           | No              | No            |

| Optimize (OPTIMIZE)              | Yes          | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | No           | No              | No            |

| Constraints P                    |              |          |           |               |                 |          |          |            |             |           |            |            |              |                 |               |

| Period (PERIOD)                  | Yes          | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | Yes          | Yes             | Yes           |

| Pin (PIN)                        | Yes          | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | No           | No              | No            |

| POST_CRC                         | No           | No       | No        | No            | No              | No       | Yes      | No         | No          | No        | Yes        | No         | No           | No              | No            |

| POST_CRC_ACTION                  | No           | No       | No        | No            | No              | No       | No       | No         | No          | No        | Yes        | No         | No           | No              | No            |

| POST_CRC_FREQ                    | No           | No       | No        | No            | No              | No       | No       | No         | No          | No        | Yes        | No         | No           | No              | No            |

Table 1-1: Supported Architectures

| Constraint                             |        |          |           |               |                 |          | Arc      | hitec      | ture        |           |            |            |              |                 |               |

|----------------------------------------|--------|----------|-----------|---------------|-----------------|----------|----------|------------|-------------|-----------|------------|------------|--------------|-----------------|---------------|

|                                        | Virtex | Virtex-E | Virtex-II | Virtex-II Pro | Virtex-II Pro X | Virtex-4 | Virtex-5 | Spartan-II | Spartan-IIE | Spartan-3 | Spartan-3A | Spartan-3E | XC9500/XL\XV | CoolRunnerXPLA3 | CoolRunner-II |

| POST_CRC_SIGNAL                        | No     | No       | No        | No            | No              | No       | Yes      | No         | No          | No        | No         | No         | No           | No              | No            |

| Priority (PRIORITY)                    | Yes    | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | Yes          | Yes             | Yes           |

| Prohibit (PROHIBIT)                    | Yes    | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | Yes          | Yes             | Yes           |

| Pulldown (PULLDOWN)                    | Yes    | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | No           | No              | No            |

| Pullup (PULLUP)                        | Yes    | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | No           | Yes             | Yes           |

| Power Mode<br>(PWR_MODE)               | No     | No       | No        | No            | No              | No       | No       | No         | No          | No        | No         | No         | Yes          | No              | No            |

| Constraints R                          |        |          |           |               |                 |          |          |            |             |           |            |            |              |                 |               |

| Registers (REG)                        | No     | No       | No        | No            | No              | No       | No       | No         | No          | No        | No         | No         | Yes          | Yes             | Yes           |

| Relative Location (RLOC)               | Yes    | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | No           | No              | No            |

| Relative Location Origin (RLOC_ORIGIN) | Yes    | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | No           | No              | No            |

| Relative Location Range (RLOC_RANGE)   | Yes    | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | No           | No              | No            |

| Constraints S                          | 111    |          | I.        |               |                 |          | <u> </u> |            |             |           | l.         | 1          |              |                 |               |

| Save Net Flag (SAVE NET FLAG)          | Yes    | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | No           | No              | No            |

| Schmitt Trigger<br>(SCHMITT_TRIGGER)   | No     | No       | No        | No            | No              | No       | No       | No         | No          | No        | No         | No         | No           | No              | Yes           |

| Slew (SLEW)                            | Yes    | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | Yes          | Yes             | Yes           |

| Slow (SLOW)                            | Yes    | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | Yes          | Yes             | Yes           |

| Stepping (STEPPING)                    | No     | No       | Yes       | Yes           | Yes             | Yes      | Yes      | No         | No          | No        | Yes        | Yes        | No           | No              | No            |

| Suspend (SUSPEND)                      | No     | No       | No        | No            | No              | No       | No       | No         | No          | No        | Yes        | No         | No           | No              | No            |

| System Jitter<br>(SYSTEM_JITTER)       | Yes    | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | No           | No              | No            |

| Constraints T                          |        |          | •         | -             |                 |          |          |            |             |           |            |            |              |                 |               |

| Temperature<br>(TEMPERATURE)           | Yes    | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | No           | No              | No            |

| Timing Ignore (TIG)                    | Yes    | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | No           | No              | No            |

| Timing Group (TIMEGRP)                 | Yes    | Yes      | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | Yes          | Yes             | Yes           |

Table 1-1: Supported Architectures

| Constraint                                        |        | Architecture |           |               |                 |          |          |            |             |           |            |            |              |                 |               |

|---------------------------------------------------|--------|--------------|-----------|---------------|-----------------|----------|----------|------------|-------------|-----------|------------|------------|--------------|-----------------|---------------|

|                                                   | Virtex | Virtex-E     | Virtex-II | Virtex-II Pro | Virtex-II Pro X | Virtex-4 | Virtex-5 | Spartan-II | Spartan-IIE | Spartan-3 | Spartan-3A | Spartan-3E | XC9500\XL\XV | CoolRunnerXPLA3 | CoolRunner-II |

| Timing Specifications (TIMESPEC)                  | Yes    | Yes          | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | Yes          | Yes             | Yes           |

| Timing Name (TNM)                                 | Yes    | Yes          | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | Yes          | Yes             | Yes           |

| Timing Name Net (TNM_NET)                         | Yes    | Yes          | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | No           | No              | No            |

| Timing Point<br>Synchronization<br>(TPSYNC)       | Yes    | Yes          | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | No           | No              | No            |

| Timing Thru Points (TPTHRU)                       | Yes    | Yes          | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | No           | No              | No            |

| Timing Specification<br>Identifier (TSidentifier) | Yes    | Yes          | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | Yes          | Yes             | Yes           |

| Constraints U                                     | -11    |              |           |               |                 | •        |          |            |             |           |            |            |              |                 |               |

| U_SET                                             | Yes    | Yes          | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | No           | No              | No            |

| Use Relative Location (USE_RLOC)                  | Yes    | Yes          | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | No           | No              | No            |

| Use Low Skew Lines<br>(USELOWSKEWLINES)           | Yes    | Yes          | No        | No            | No              | No       | No       | Yes        | Yes         | No        | No         | No         | No           | No              | No            |

| Constraints V-X                                   | -11    |              | ı         |               |                 |          |          | H.         |             | H.        |            |            |              |                 |               |

| VCCAUX                                            | No     | No           | No        | No            | No              | No       | No       | No         | No          | No        | Yes        | No         | No           | No              | No            |

| Voltage (VOLTAGE)                                 | Yes    | Yes          | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | No           | No              | No            |

| VREF                                              | No     | No           | No        | No            | No              | No       | No       | No         | No          | No        | No         | No         | No           | No              | Yes           |

| Wire And (WIREAND)                                | No     | No           | No        | No            | No              | No       | No       | No         | No          | No        | No         | No         | Yes          | No              | No            |

| XBLKNM                                            | Yes    | Yes          | Yes       | Yes           | Yes             | Yes      | Yes      | Yes        | Yes         | Yes       | Yes        | Yes        | No           | No              | No            |

# Constraint Types

This chapter discusses the various types of constraints documented within this Guide. This chapter contains the following sections:

- "Attributes and Constraints"

- "CPLD Fitter"

- "Grouping Constraints"

- "Logical Constraints"

- "Physical Constraints"

- "Mapping Directives"

- "Placement Constraints"

- "Routing Directives"

- "Synthesis Constraints"

- "Timing Constraints"

- "Configuration Constraints"

#### **Attributes and Constraints**

The terms *attribute* and *constraint* have been used interchangeably by some in the engineering community, while others ascribe different meanings to these terms. In addition, language constructs use the terms *attribute* and *directive* in similar yet different senses. For the purpose of clarification, the Xilinx® documentation refers to the terms *attributes* and *constraints* as defined below.

#### **Attributes**

An attribute is a property associated with a device architecture primitive component that generally affects an instantiated component's functionality or implementation. Attributes are passed as follows:

- In VHDL, by means of generic maps

- In Verilog, by means of defparams or inline parameter passing while instantiating the primitive component

Examples of attributes are:

- The INIT property on a LUT4 component

- The CLKFX\_DIVIDE property on a DCM

All attributes are described in the appropriate Xilinx *Libraries Guide* as a part of the primitive component description.

#### Synthesis Constraints

Synthesis constraints direct the synthesis tool optimization technique for a particular design or piece of HDL code. They are either embedded within the VHDL or Verilog code, or within a separate synthesis constraints file. Examples of synthesis constraints are:

- USE\_DSP48 (XST)

- RAM\_STYLE (XST)

Synthesis constraints are documented as follows:

- XST constraints are documented in the Xilinx XST User Guide.

- Synthesis constraints for other synthesis tools are documented in the vendor's

documentation for the tool. For more information on synthesis constraints for your

synthesis tool, see the vendor documentation.

#### Implementation Constraints

Implementation constraints are instructions given to the FPGA implementation tools to direct the mapping, placement, timing or other guidelines for the implementation tools to follow while processing an FPGA design. Implementation constraints are generally placed in the UCF file, but may exist in the HDL code, or in a synthesis constraints file. Examples of implementation constraints are:

- LOC (placement) constraints

- PERIOD (timing) constraints

Implementation constraints are documented in the Xilinx Constraints Guide.

#### **CPLD Fitter**

The following constraints apply to CPLD devices:

| "BUFG (CPLD)"                                     | "Collapse (COLLAPSE)"                  | "CoolCLOCK<br>(COOL_CLK)"  |

|---------------------------------------------------|----------------------------------------|----------------------------|

| "Data Gate (DATA_GATE)"                           | "Fast (FAST)"                          | "Input Registers (INREG)"  |

| "Input Output Standard<br>(IOSTANDARD)"           | "Keep (KEEP)"                          | "Keeper (KEEPER)"          |

| "Location (LOC)"                                  | "Maximum Product Terms (MAXPT)"        | "No Reduce<br>(NOREDUCE)"  |

| "Offset In (OFFSET IN)" "Offset Out (OFFSET OUT)" | "Open Drain<br>(OPEN_DRAIN)"           | "Period (PERIOD)"          |

| "Prohibit (PROHIBIT)"                             | "Pullup (PULLUP)"                      | "Power Mode<br>(PWR_MODE)" |

| "Registers (REG)"                                 | "Schmitt Trigger<br>(SCHMITT_TRIGGER)" | "Slow (SLOW)"              |

| "Timing Group<br>(TIMEGRP)"                       | "Timing Specifications (TIMESPEC)"     | "Timing Name (TNM)"        |

"Timing Specification Identifier (TSidentifier)"

"VREF"

"Wire And (WIREAND)"

# **Grouping Constraints**

In a TS TIMESPEC attribute, specify the set of paths to be analyzed by grouping start and end points in one of the following ways.

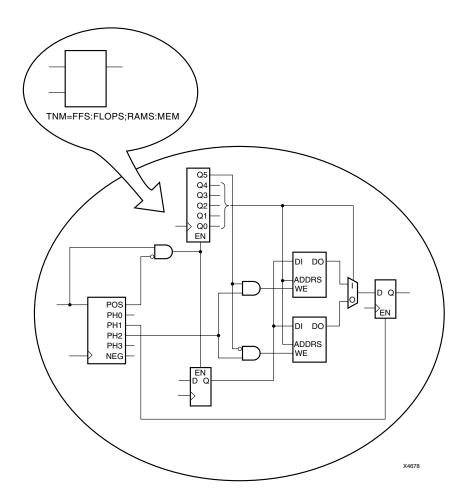

- Refer to a predefined group by specifying one of the corresponding keywords: CPUS, DSPS, FFS, HSIOS, LATCHES, MULTS, PADS, RAMS, BRAMS\_PORTA, or BRAMS\_PORTB.

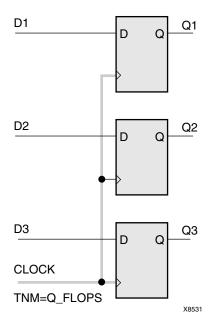

- Create your own groups within a predefined group by tagging symbols with "Timing Name (TNM)" (pronounced tee-name) and "Timing Name Net (TNM\_NET)" constraints.

- Create groups that are combinations of existing groups using "Timing Group (TIMEGRP)" symbols.

- Create groups by pattern matching on net names. For more information, see "Creating Groups by Pattern Matching" in the "Timing Group (TIMEGRP)" constraint.

#### **Using Predefined Groups**

Using predefined groups, you can refer to a group of flip-flops, input latches, pads, or RAMs by using the corresponding keywords. See the following table.

Table 2-1: Predefined Groups

| Keyword     | Description                                                                                                     |

|-------------|-----------------------------------------------------------------------------------------------------------------|

| CPUS        | PPC405 in Virtex <sup>TM</sup> -II Pro, Virtex-II Pro X and Virtex-4 FX                                         |

| DSPS        | DSP48 and any DSP48 derivative in Virtex-4, Virtex-5 and Spartan-3A Extended                                    |

| FFS         | All CLB and IOB edge-triggered flip-flops                                                                       |

|             | Shift Register LUTs in Virtex and derived                                                                       |

|             | <ul> <li>Dual-data-rate registers in Virtex-II and derived (includes both<br/>flip-flops in the DDR)</li> </ul> |

| HSIOS       | GT and GT10 in Virtex-II Pro and Virtex-II Pro X                                                                |

| LATCHES     | All CLB and IOB level-sensitive latches                                                                         |

| MULTS       | Multipliers, both sync and async, in Virtex-II and derived                                                      |

| PADS        | All I/O pads (typically inferred from top level HDL ports)                                                      |

| RAMS        | All CLB LUT RAMs, both single- and dual-port (includes both ports of dual-port)                                 |

|             | All block RAMs, both single-and dual-port (includes both ports of dual-port)                                    |

| BRAMS_PORTA | Port A of all dual-port block RAMs                                                                              |

| BRAMS_PORTB | Port B of all dual-port block RAMs                                                                              |

From-To statements enable you to define timing specifications for paths between predefined groups. The following examples are TS attributes that are entered in the UCF. This method enables you to easily define default timing specifications for the design, as illustrated by the following examples.

#### **Predefined Group Examples**

Following is a UCF syntax example.

```

TIMESPEC "TS01"=FROM FFS TO FFS 30;

TIMESPEC "TS02"=FROM LATCHES TO LATCHES 25;

TIMESPEC "TS03"=FROM PADS TO RAMS 70;

TIMESPEC "TS04"=FROM FFS TO PADS 55;

TIMESPEC "TS01" = FROM BRAMS_PORTA TO BRAMS_PORTB(gork*);

```

For BRAMS\_PORTA and BRAM\_PORTB, the specification TS01 controls paths that begin at any A port and end at a B port, which drives a signal matching the pattern **gork\***.

#### BRAMS\_PORTA and BRAMS\_PORTB Examples

Following are additional examples of BRAMS\_PORTA and BRAMS\_PORTB.

```

NET "X" TNM_NET = BRAMS_PORTA groupA;

```

The TNM group group A contains all A ports that are driven by net X. If net X is traced forward into any B port inputs, any single-port block RAM elements, or any Select RAM elements, these do not become members of group A.

```

NET "X" TNM_NET = BRAMS_PORTB( dob* ) groupB;

```

The TNM group groupB contains each B port driven by net X, if at least one output on that B port drives a signal matching the pattern dob\*.

```

INST "Y" TNM = BRAMS_PORTB groupC;

```

The TNM group groupC contains all B ports found under instance Y. If instance Y is itself a dual-port block RAM primitive, then groupC contains the B port of that instance.

```

INST "Y" TNM = BRAMS_PORTA( doa* ) groupD;

```

The TNM group group D contains each A port found under instance Y, if at least one output on that A port drives a signal matching the pattern doa\*.

```

TIMEGRP "groupE" = BRAMS_PORTA;

```

The user group groupE contains the A ports of all dual-port block RAM elements in the design. This is equivalent to BRAMS\_PORTA(\*).

```

TIMEGRP "groupF" = BRAMS_PORTB( mem/dob* );

```

The user group groupF contains all B ports in the design, which drives a signal matching the pattern mem/dob\*.

A predefined group can also carry a name qualifier. The qualifier can appear any place the predefined group is used. This name qualifier restricts the number of elements referred to. The syntax is:

```

predefined group (name_qualifier [ name_qualifier ])

```

*name\_qualifier* is the full hierarchical name of the net that is sourced by the primitive being identified.

The name qualifier can include the following wildcard characters:

- An asterisk (\*) to show any number of characters

- A question mark (?) to show a single character

Wildcard characters allow you to:

- Specify more than one net

- Shorten and simplify the full hierarchical name

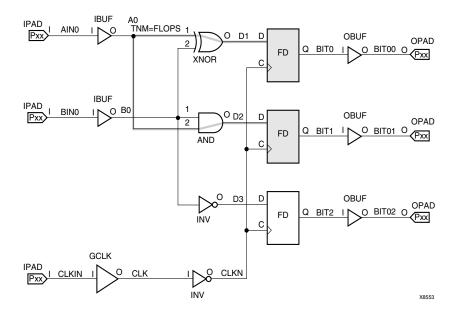

For example, specifying the group FFS(MACRO\_A/Q?) selects only the flip-flops driving the Q0, Q1, Q2 and Q3 nets.

The following constraints are grouping constraints:

| "Component Group<br>(COMPGRP)" | "Pin (PIN)"                 | "Timing Group (TIMEGRP)"                      |

|--------------------------------|-----------------------------|-----------------------------------------------|

| "Timing Name (TNM)"            | "Timing Name Net (TNM_NET)" | "Timing Point<br>Synchronization<br>(TPSYNC)" |

| "Timing Thru Points (TPTHRU)"  |                             |                                               |

# **Logical Constraints**

Logical constraints are constraints that are attached to elements in the design prior to mapping or fitting. Applying logical constraints helps you to adapt your design's performance to expected worst-case conditions. Later, when you choose a specific Xilinx® architecture, and place and route or fit your design, the logical constraints are converted into physical constraints.

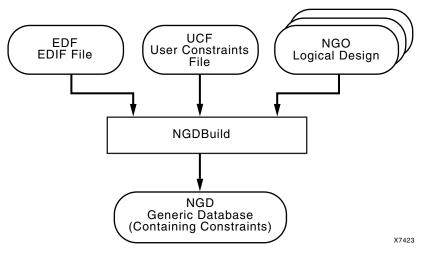

You can attach logical constraints using attributes in the input design, which are written into the Netlist Constraints File (NCF) or NGC netlist, or with a User Constraints File (UCF).

Three categories of logical constraints are:

- "Placement Constraints"

- "Relative Location (RLOC) Constraints"

- "Timing Constraints"

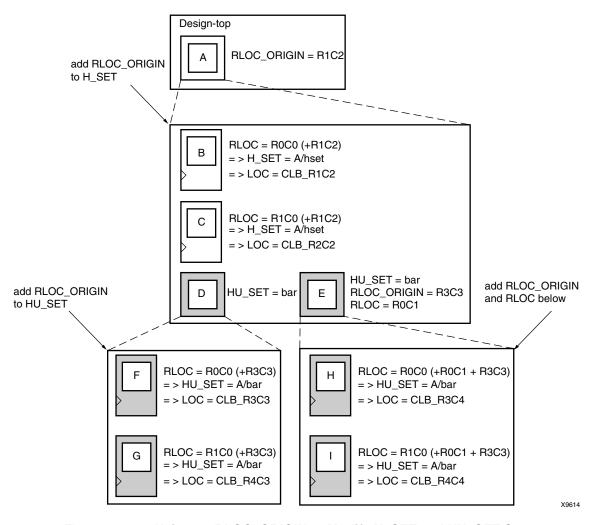

For FPGA devices, relative location constraints (RLOCs) group logic elements into discrete sets. They allow you to define the location of any element within the set relative to other elements in the set, regardless of eventual placement in the overall design. For more information, see "Relative Location (RLOC) Constraints" in this chapter.

Timing constraints allow you to specify the maximum allowable delay or skew on any given set of paths or nets in your design.

# **Physical Constraints**

Constraints can also be attached to the elements in the physical design, that is, the design after mapping has been performed. These constraints are referred to as physical constraints. They are defined in the Physical Constraints File (PCF), which is created during mapping.

Constraints Guide <a href="https://www.xilinx.com">www.xilinx.com</a> 21

Xilinx recommends that you place any user-generated constraint in the UCF file, not in an NCF or PCF file.

**Note:** The information in this section applies to FPGA device families only.

When a design is mapped, the logical constraints found in the netlist and the UCF file are translated into physical constraints, that is, constraints that apply to a specific architecture. These constraints are found in a mapper-generated file called the Physical Constraints File (PCF).

The PCF file contains two sections:

- The schematic section, which contains the physical constraints based on the logical constraints found in the netlist and the UCF file

- The user section, which can be used to add any physical constraints

# **Mapping Directives**

Mapping directives instruct the mapper to perform specific operations. The following constraints are mapping directives:

| "Area Group<br>(AREA_GROUP)"             | "BEL"                                        | "Block Name (BLKNM)"                    |

|------------------------------------------|----------------------------------------------|-----------------------------------------|

| "DCI_VALUE"                              | "D rive (DRIVE)"                             | "Fast (FAST)"                           |

| "Hierarchical Block Name (HBLKNM)"       | "Hierarchical Lookup Table<br>Name (HLUTNM)" | "HU_SET"                                |

| "IOB"                                    | "Input Output Block Delay (IOBDELAY)"        | "Input Output Standard<br>(IOSTANDARD)" |

| "Keep (KEEP)"                            | "Keeper (KEEPER)"                            | "Lookup Table Name<br>(LUTNM)"          |

| "Map (MAP)"                              | "No Delay (NODELAY)"                         | "Optimize (OPTIMIZE)"                   |

| "Pulldown<br>(PULLDOWN)"                 | "Pullup (PULLUP)"                            | "Relative Location (RLOC)"              |

| "Relative Location Origin (RLOC_ORIGIN)" | "Relative Location Range (RLOC_RANGE)"       | "Save Net Flag (SAVE NET FLAG)"         |

| "Slew (SLEW)"                            | "U_SET"                                      | "Use Relative Location (USE_RLOC)"      |

| ((2/D) T/2 D T/                          |                                              |                                         |

#### **Placement Constraints**

This section describes the placement constraints for each type of logic element in FPGA designs, such as:

Flip-flops

"XBLKNM"

- ROMs and RAMs

- BUFTs

- CLBs

- IOBs

- I/Os

- Edge decoders

- Global buffers

Individual logic gates, such as AND or OR gates, are mapped into CLB function generators before the constraints are read, and therefore cannot be constrained.

The following constraints control mapping and placement of symbols in a netlist:

- "Block Name (BLKNM)"

- "Hierarchical Block Name (HBLKNM)"

- "Hierarchical Lookup Table Name (HLUTNM)"

- "Location (LOC)"

- "Lookup Table Name (LUTNM)"

- "Prohibit (PROHIBIT)"

- "Relative Location (RLOC)"

- "Relative Location Origin (RLOC\_ORIGIN)"

- "Relative Location Range (RLOC\_RANGE)"

- "XBLKNM"

Most constraints can be specified either in the HDL or in the UCF file. In a constraints file, each placement constraint acts upon one or more symbols. Every symbol in a design carries a unique name, which is defined in the input file. Use this name in a constraint statement to identify the symbol.

The UCF and NCF files are case sensitive. Identifier names (names of objects in the design, such as net names) must exactly match the case of the name as it exists in the source design netlist. However, any Xilinx constraint keyword (for example, LOC, PROHIBIT, RLOC, BLKNM) can be entered in either all upper-case or all lower-case letters. Mixed case is not allowed.

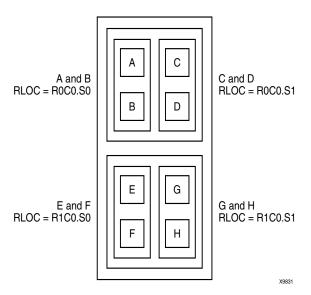

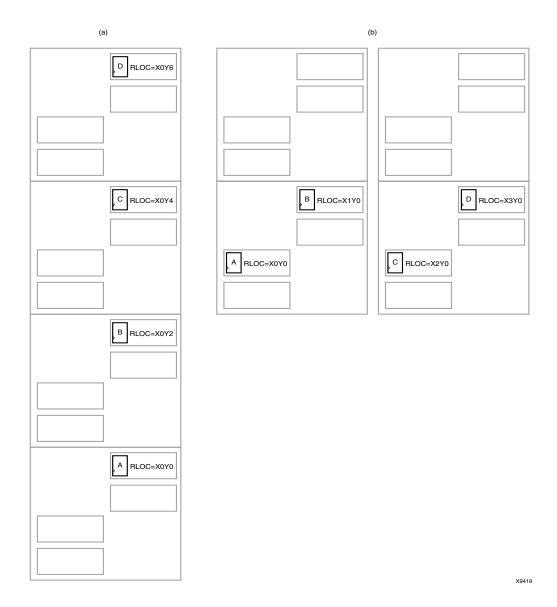

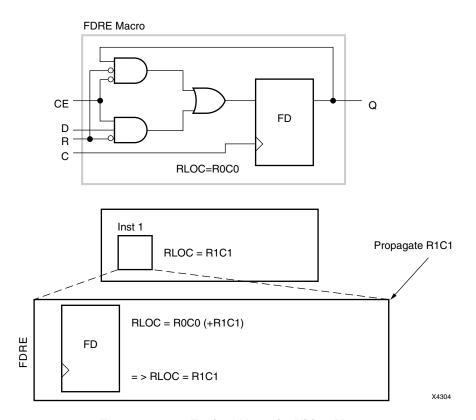

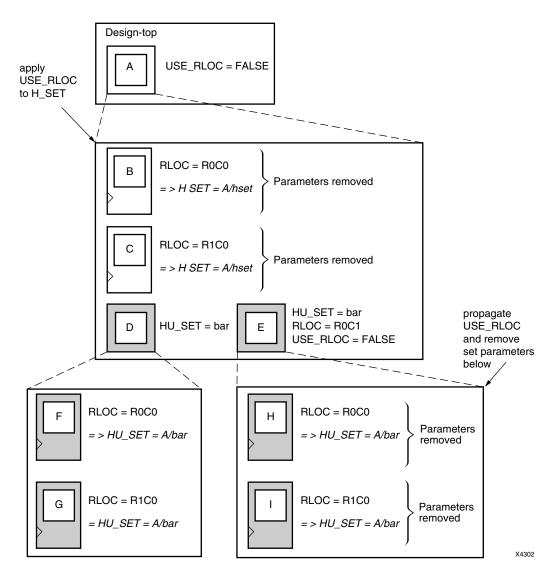

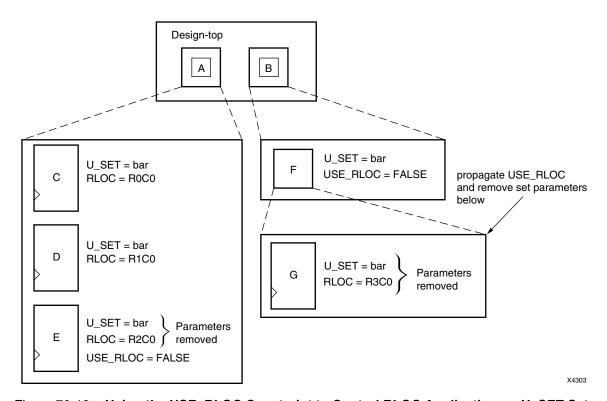

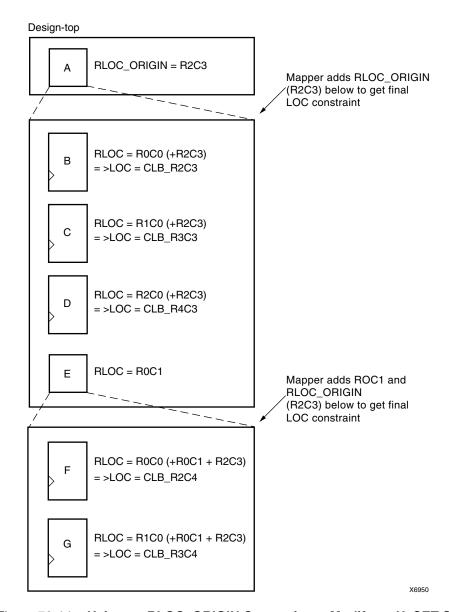

#### Relative Location (RLOC) Constraints

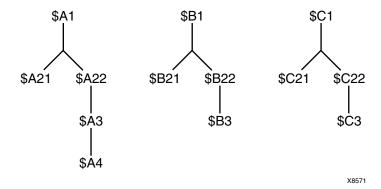

The RLOC constraint groups logic elements into discrete sets. You can define the location of any element within the set relative to other elements in the set, regardless of eventual placement in the overall design. For example, if RLOC constraints are applied to a group of eight flip-flops organized in a column, the mapper maintains the columnar order and moves the entire group of flip-flops as a single unit. In contrast, absolute location (LOC) constraints constrain design elements to specific locations on the FPGA die with no relation to other design elements.

#### **Placement Constraints**

The following constraints are placement constraints:

| "Area Group<br>(AREA_GROUP)"       | "BEL"                                    | "Location (LOC)"                       |

|------------------------------------|------------------------------------------|----------------------------------------|

| "Locate (LOCATE)"                  | "Optimizer Effort<br>(OPT_EFFORT)"       | "Prohibit (PROHIBIT)"                  |

| "Relative Location<br>(RLOC)"      | "Relative Location Origin (RLOC_ORIGIN)" | "Relative Location Range (RLOC_RANGE)" |

| "Use Relative Location (USE_RLOC)" |                                          |                                        |

# **Routing Directives**

Routing directives instruct PAR to perform specific operations. The following constraints are routing directives:

- Area Group (AREA\_GROUP)

- Configuration Mode (CONFIG\_MODE)

- Lock Pins (LOCK\_PINS)

- Optimizer Effort (OPT\_EFFORT)

- Use Low Skew Lines (USELOWSKEWLINES)

# **Synthesis Constraints**

Synthesis constraints instruct the synthesis tool to perform specific operations. The following constraints are synthesis constraints:

| "From To (FROM-TO)"   | "IOB"                                             | "Keep (KEEP)"               |

|-----------------------|---------------------------------------------------|-----------------------------|

| "Map (MAP)"           | "Offset In (OFFSET IN)" "Offset Out (OFFSET OUT)" | "Period (PERIOD)"           |

| "Timing Ignore (TIG)" | "Timing Name (TNM)"                               | "Timing Name Net (TNM_NET)" |

# **Timing Constraints**

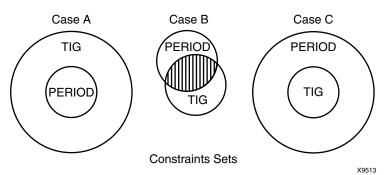

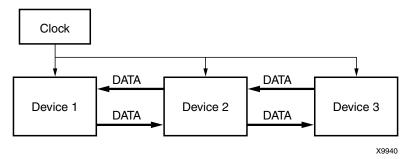

Xilinx software enables you to specify precise timing constraints for your Xilinx designs. You can specify the timing constraints for any nets or paths in your design, or you can specify them globally. One way of specifying path requirements is to first identify a set of paths by identifying a group of start and end points. The start and end points can be flipflops, I/O pads, latches, or RAMs. You can then control the worst-case timing on the set of paths by specifying a single delay requirement for all paths in the set.

The primary way to specify timing constraints is to enter them in your design (HDL and schematic). However, you can also specify timing constraints in constraints files (UCF, NCF, PCF, XCF). For more information about each constraint, see the later chapters in this Guide.

Once you define timing specifications and map the design, PAR places and routes your design based on these requirements.

To analyze the results of your timing specifications, use the command line tool, TRACE (TRCE) or the ISE<sup>TM</sup> Timing Analyzer.

#### XST Timing Constraints

XST supports an XCF (XST Constraints File) syntax to define synthesis and timing constraints. The constraint syntax in use prior to the ISE 7.1i release is no longer supported.

Timing constraints supported by XST can be applied via either:

- The **-glob\_opt** command line switch

- The constraints file

#### Command Line Switch

Using the <code>-glob\_opt</code> command line switch is the same as selecting **Process Properties** > **Synthesis Options** > **Global Optimization Goal**. Using this method allows you to apply global timing constraints to the entire design. You cannot specify a value for these constraint; XST optimizes them for the best performance. These constraints are overridden by constraints specified in the constraints file.

#### Constraints File

Using the constraint file method, you can use the native UCF timing constraint syntax. Using the XCF syntax, XST supports constraints such as TNM\_NET, TIMEGRP, PERIOD, TIG, FROM-TO, including wildcards and hierarchical names.

**Note:** Timing constraints are written to the NGC file only when the Write Timing Constraints property is checked in the Process Properties dialog box in Project Navigator, or the - write\_timing\_constraints option is specified when using the command line. By default, they are not written to the NGC file.

Independent of the way timing constraints are specified, the Clock Signal option affects timing constraint processing. In the case where a clock signal goes through which input pin is the real clock pin. The CLOCK\_SIGNAL constraint allows you to define the clock pin. For more information, see the Xilinx XST User Guide.

# **UCF Timing Constraint Support**

**Caution!** If you specify timing constraints in the XCF file, Xilinx strongly suggests that you to use the '/' character as a hierarchy separator instead of '\_'.

The following timing constraints are supported in the XST Constraints File (XCF).

#### From-To

FROM-TO defines a timing constraint between two groups. A group can be user-defined or predefined (FFS, PADS, RAMS). For more information, see the "From To (FROM-TO)" constraint. Following is an example of XCF Syntax:

```

TIMESPEC "TSname"=FROM "group1" TO "group2" value;

```

#### **OFFSET IN**

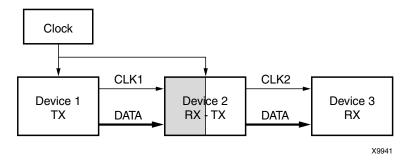

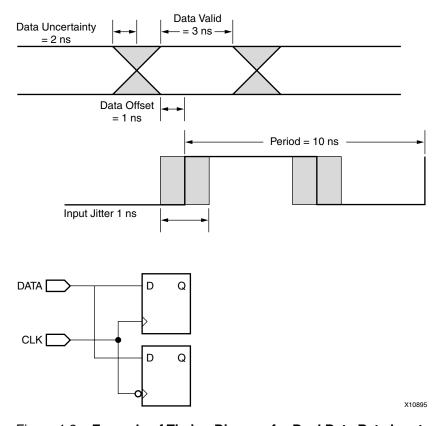

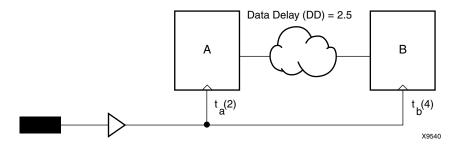

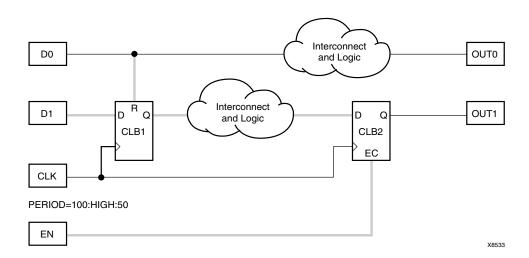

The OFFSET IN constraint is used to specify the timing requirements of an input interface to the FPGA. The constraint specifies the clock and data timing relationship at the external pads of the FPGA. An OFFSET IN constraint specification checks the setup and hold timing requirements of all synchronous elements associated with the constraint. The following image shows the paths covered by the OFFSET IN constraint. For more information, see the "Offset In (OFFSET IN)" constraint.

#### **OFFSET OUT**

The OFFSET OUT constraint is used to specify the timing requirements of an output interface from the FPGA. The constraint specifies the time from the clock edge at the input pin of the FPGA until data becomes valid at the outp pin of the FPGA. For more information, see the "Offset Out (OFFSET OUT)" constraint.

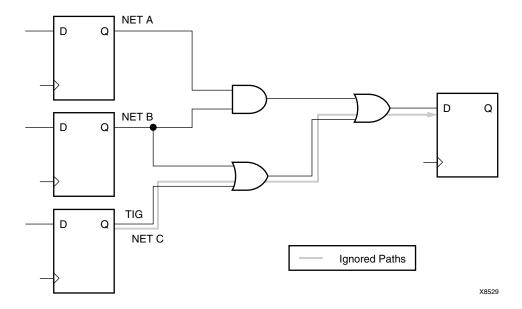

#### TIG

The "Timing Ignore (TIG)" constraint causes all paths going through a specific net to be ignored for timing analyses and optimization purposes. This constraint can be applied to the name of the signal affected.

XCF Syntax:

```

NET "netname" TIG;

```

#### **TIMEGRP**

"Timing Group (TIMEGRP)" is a basic grouping constraint. In addition to naming groups using the TNM identifier, you can also define groups in terms of other groups. You can create a group that is a combination of existing groups by defining a TIMEGRP constraint.

You can place TIMEGRP constraints in a constraints file (XCF or NCF). You can use TIMEGRP attributes to create groups using the following methods.

- Combining multiple groups into one

- Defining flip-flop subgroups by clock sense

XCF Syntax:

```

TIMEGRP "newgroup"="existing_grp1" "existing_grp2"

["existing_grp3" . . .];

```

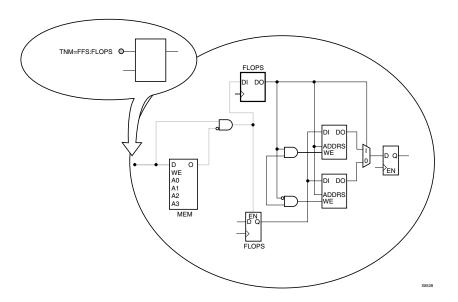

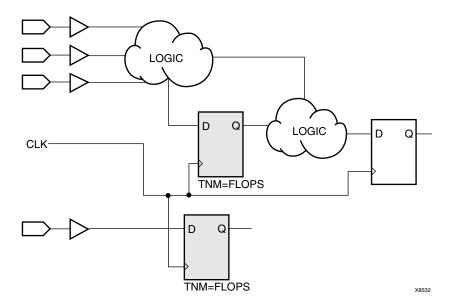

#### **TNM**

"Timing Name (TNM)" is a basic grouping constraint. Use TNM (Timing Name) to identify the elements that make up a group, which you can then use in a timing specification. TNM tags specific FFS, RAMs, LATCHES, PADS, BRAMS\_PORTA, BRAMS\_PORTB, CPUS, HSIOS, and MULTS as members of a group to simplify the application of timing specifications to the group.

The RISING and FALLING keywords may also be used with TNMs.

XCF Syntax:

```

{NET | INST | PIN } "net_or_pin_or_inst_name" TNM=[predefined_group]

identifier;

```

#### TNM Net

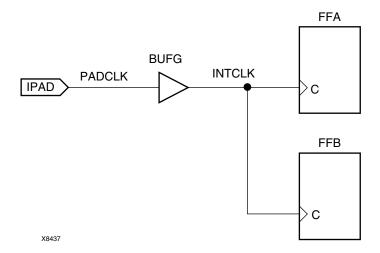

"Timing Name Net (TNM\_NET)" is essentially equivalent to TNM on a net *except* for input pad nets. Special rules apply when using TNM\_NET with the "Period (PERIOD)" constraint for DLL/DCM/PLLs in the following devices:

- Virtex

- Virtex-E

- Virtex-II

- Virtex-II Pro

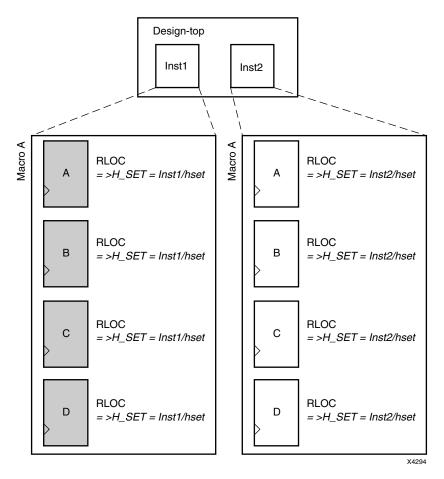

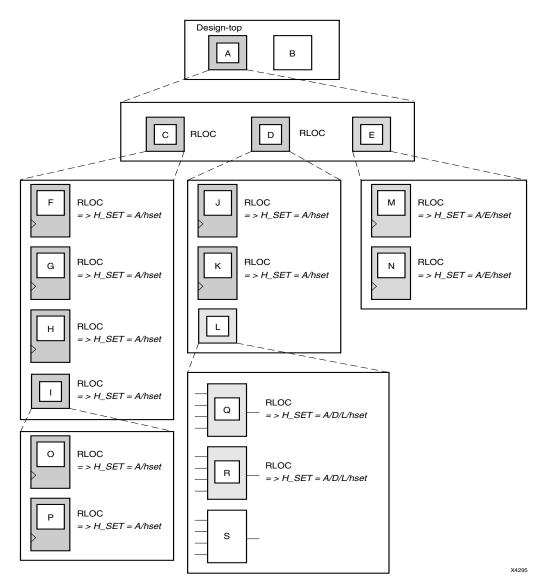

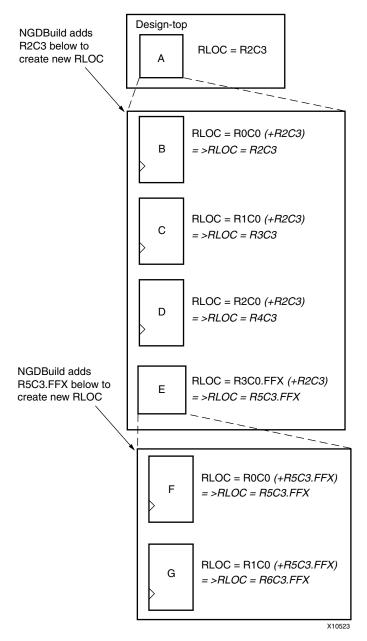

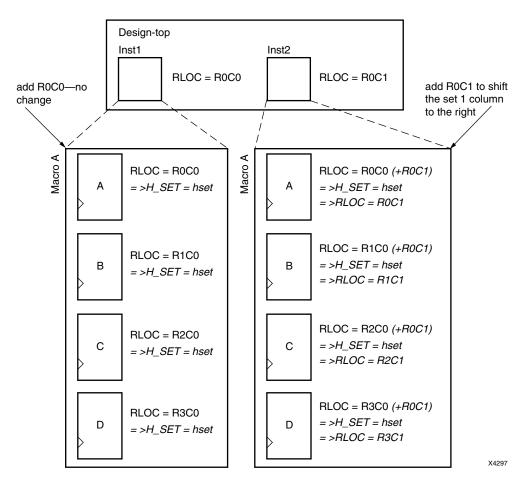

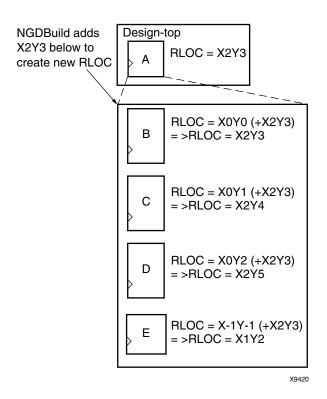

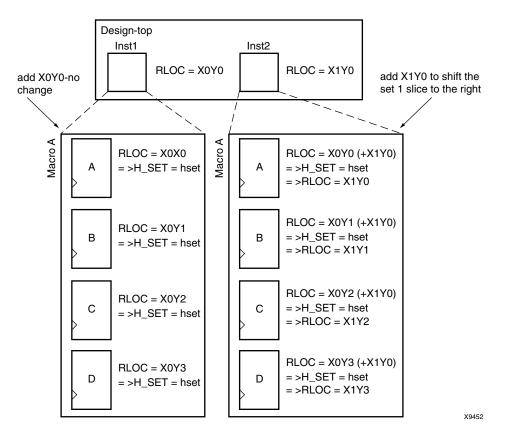

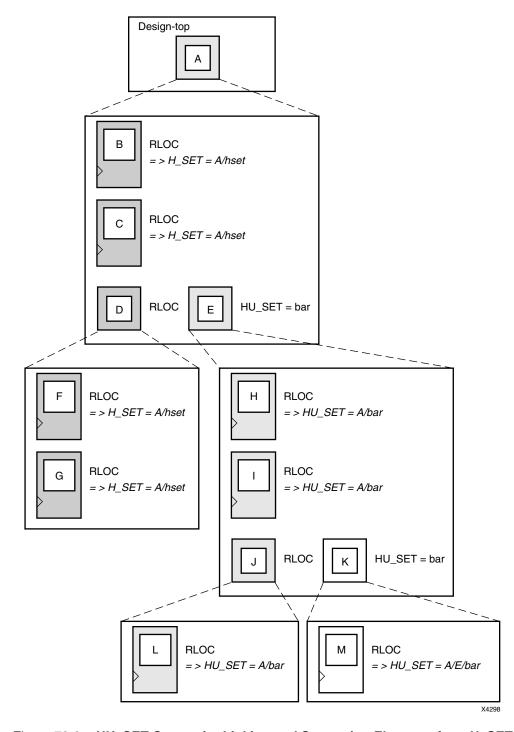

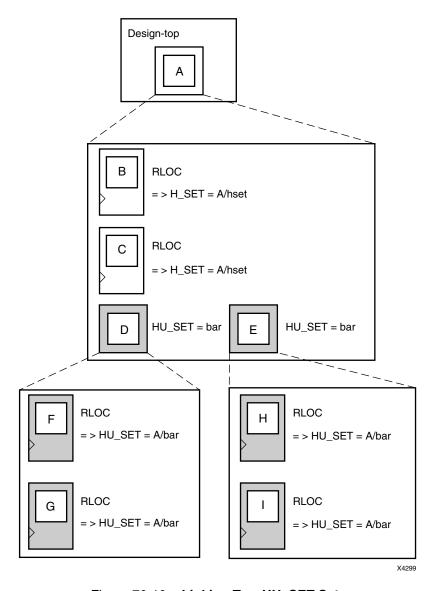

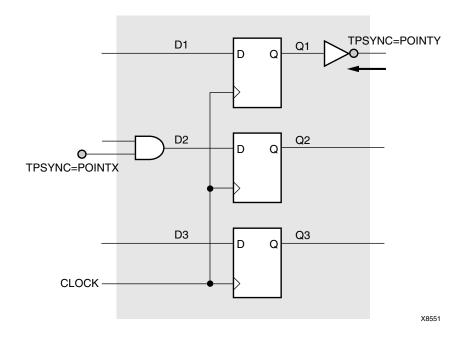

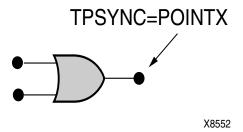

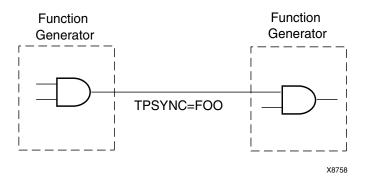

- Virtex-II Pro X