Podstawy układów mikroelektronicznych - laboratorium

dla kierunku

Technologie Kosmiczne i Satelitarne, studia stacjonarne 2 st.

Ćwiczenie nr 3 „Projekt topografii sumatora 4-bitowego CMOS”

1. Wstęp

Celem ćwiczenia jest wykonanie projektu topografii sumatora

4-bitowego CMOS. Należy wykorzystać sumator zaprojektowane w poprzednim

ćwiczeniu nr 2.

2. Uruchomienie programu

Sala 308

Program MAGIC uruchamia się dwuetapowo poprzez uruchomienie

najpierw Start/Programy/Cygwin-X/XWin Server a następnie wpisanie polecenia magic w terminalu, który pojawia się po

wydaniu poprzedniego polecenia.

3. Projektowany sumator

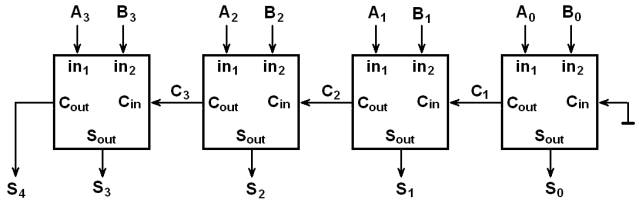

Schemat sumatora 4-bitowego pokazano na rys. 4. Należy zastosować nazwy węzłów jak na rys. 4.

Rys. 4. Sumator 4-bitowy.

4. Zadania do wykonania

W ramach ćwiczenia należy wykonać następujące czynności:

1) Wykonać projekt

topografii zgodny z technologią CMOS 0.5-µm firmy AMIS, opcja C5. Należy

wykorzystać topografię z ćw. 2. Plik nazwać ADDER4bit.mag.

Uwaga!

Projekt topografii sumatora 4 bitowego należy wykonać hierarchicznie. W tym

celu należy załadować topografię sumatora 1 bitowego w sposób hierarchiczny tj.

w konsoli magica wydać polecenie getcell ADDER1bit. Załadowanie powtórzyć 4

razy.

2)

Wykonać

ekstrakcję topografii.

3)

Wykonać

test symulacyjny (test pod kątem poprawności dodawania) zaprojektowanego

sumatora.

Plik symulacyjny do testu ADDER4bit_test.cir

4)

Wykonać

test szybkościowy sumatora.

Przyjąć, że stan niski (Low) odpowiada napięciom od 0 V do 0.5 V, a stan wysoki

(High) napięciom od 2.5 V do 3 V.

Pliki do testów:

ADDER4bit_speed_test_100MHz.cir

ADDER4bit_speed_test_300MHz.cir

ADDER4bit_speed_test_500MHz.cir

ADDER4bit_speed_test_800MHz.cir

ADDER4bit_speed_test_1GHz.cir