Strona główna

|

Katedra Systemów Mikroelektronicznych,

Wydział Elektroniki,

Telekomunikacji i Informatyki, Politechnika Gdańska

|

|

Zintegrowany analizator Chipscope

Zadanie:

Za pomocą analizatora logicznego należy zbadać działanie nieznanego bloku cyfrowego i

określić funkcję jaką on realizuje.

Dany jest blok DUT (rys.1), o którym tylko wiadomo, że:

- jest to układ kombinacyjny;

- posiada 8-bitowe wejście danych data_i (liczba dziesiętna zakodowana dwójkowo, bez znaku);

- posiada 8-btowe wyjście danych data_o(liczba dziesiętna zakodowana dwójkowo, bez znaku);

- posiada 1-bitowe wyjście błędu err_o(przepełnienia);

- dane z wyjścia data_o są linową transformacją danych z wejścia data_i.

data_o = a*data_i + b,

gdzie data_o oraz data_i są 8-bitowymi liczbami dziesiętnymi bez znaku,

a oraz b są stałymi liczbami całkowitymi.

Celem zadania jest znalezienie wartości a oraz b.

Rys. 1 Blok DUT

Procedura postępowania:

Utworzenie środowiska pracy testowanego bloku

Aby zbadać blok DUT, należy najpierw stworzyć środowisko jego pracy.

Do wejścia bloku DUT należy doprowadzić sygnał testowy, pochodzący np. z licznika.

Wyjście z bloku DUT należy podłączyć do diod LED, wyjście błędu można podłączyć do

jednej z cyfr wyświetlacza 7-segmentowego LED (pozostałe cyfry LED zostały wygaszone;

w przypadku innego wykorzystania wyświetlacza LED, należy odpowiednio zmodyfikować plik

ucf zamieszczony na końcu tej strony).

Proponowany schemat układu przedstawiono na rys. 2.

Rys. 2 Proponowany schemat blokowy układu testowania DUT

Blok DUT jest dostarczany w postaci zsyntezowanej.

Plik dut.ngc należy odpowiednio dodać do projektu. Aby to zrobić, należy:

należy odpowiednio dodać do projektu. Aby to zrobić, należy:

- Zadeklarować komponent dut w kodzie VHDL oraz osadzić go i odpowiednio podłączyć.

- Skopiować plik dut.ngc to głównego folderu projektu.

Deklaracja tego bloku wygląda następująco:

component dut is

port ( data_i : in STD_LOGIC_VECTOR (7 downto 0);

data_o : out STD_LOGIC_VECTOR (7 downto 0);

err_o : out STD_LOGIC);

end component;

Weryfikacja działania układu na diodach LED przy zwolnionym zegarze

Wykonać implementację układu z rys. 2, ustawiając wewnętrzny zegar clk na niską częstotliwość,

np. 1Hz.

Zaobserwować świecenie diod oraz działanie sygnału err na wyświetlaczu LED.

Wstawienie analizatora logicznego do układu

Do układu wstaw analizator Chipscope, składający się z dwóch bloków:

- analizatora logicznego (ILA);

- kontrolera ICON (umożliwia on podłączenie kilku bloków ILA).

Analizator Chipscope wprogramowany w układ FPGA zapisuje obserwowane sygnały do

wewnętrznej pamięci RAM. Program Chipscope Analyzer uruchomiony na komputerze PC

łączy się poprzez JTAG z analizatorem w FPGA i pobiera dane zgromadzone w pamięci RAM,

a następnie wyświetla je na ekranie komputera.

Analizator posiada zaawansowane możliwości wyzwalania.

W tym ćwiczeniu wykorzystane zostaną tylko podstawowe możliwości.

Czynności:

-

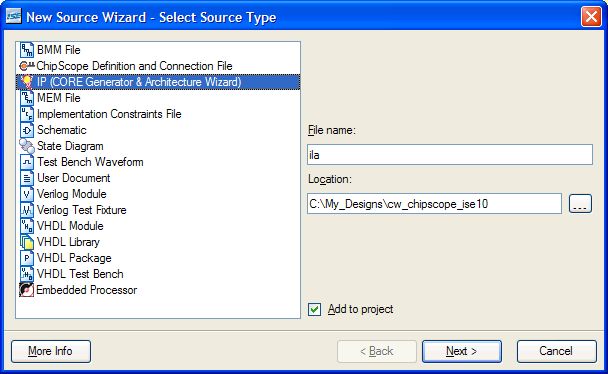

Do projektu należy dodać blok ILA korzystając z Coregenerator.

Rys. 3 Wstawianie nowych bloków

-

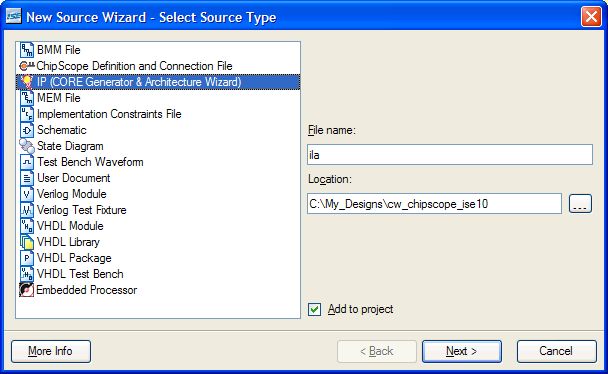

Wybrać Source Type: IP (CORE Generator & Architecture Wizard) i wpisać nazwę.

Rys. 4 Wybranie Coregeneratora

-

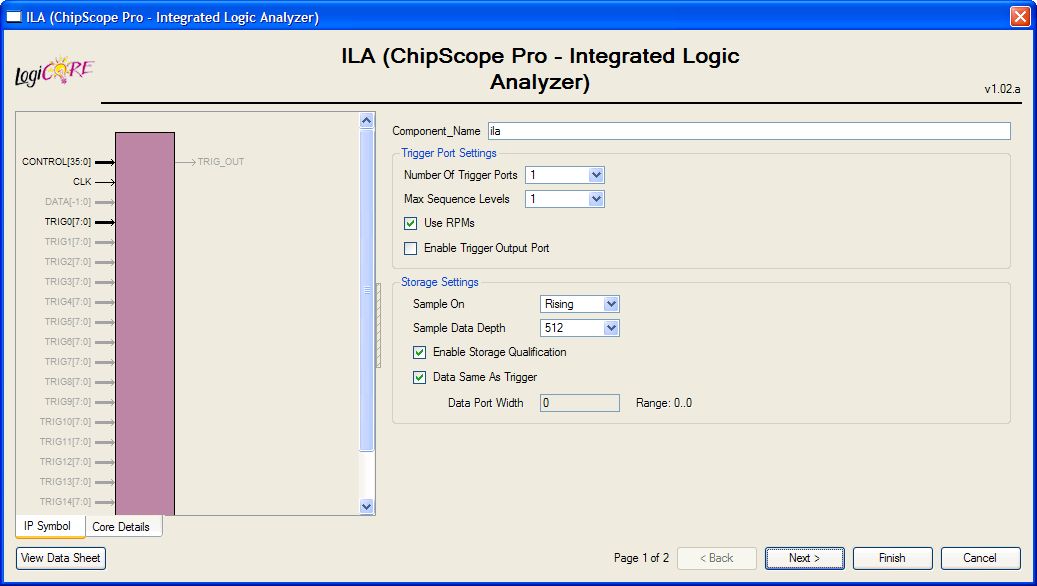

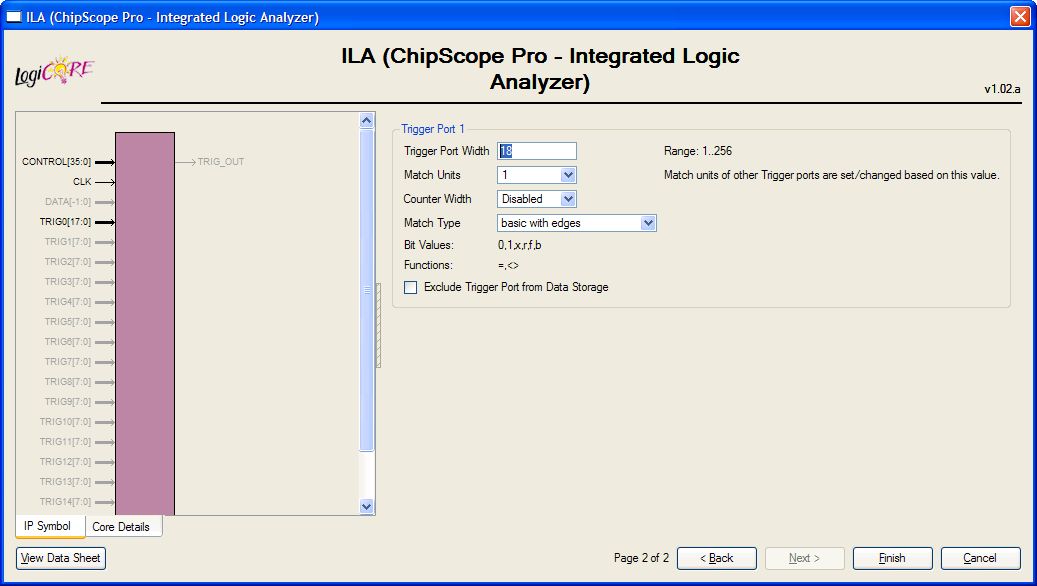

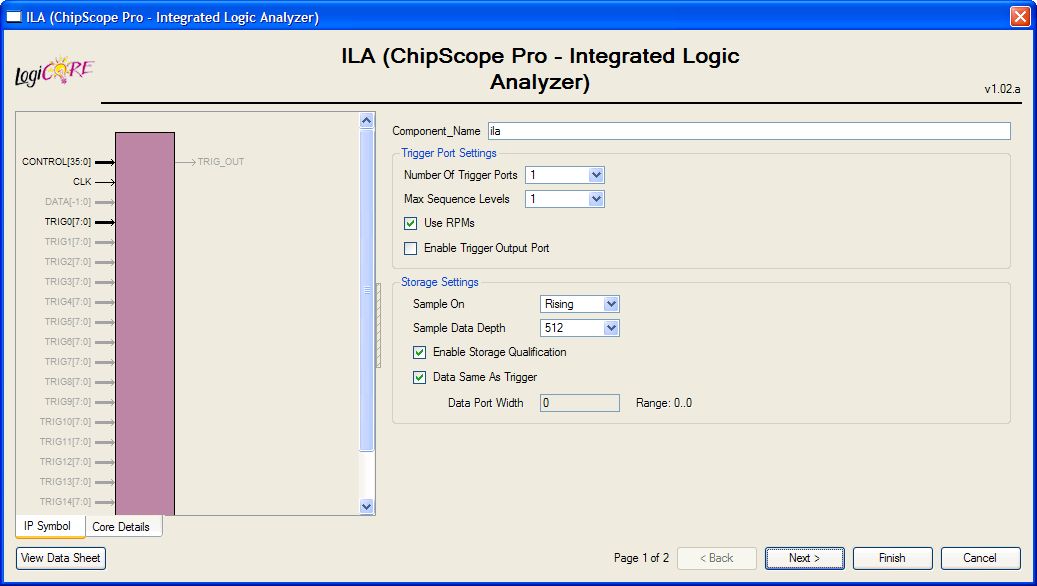

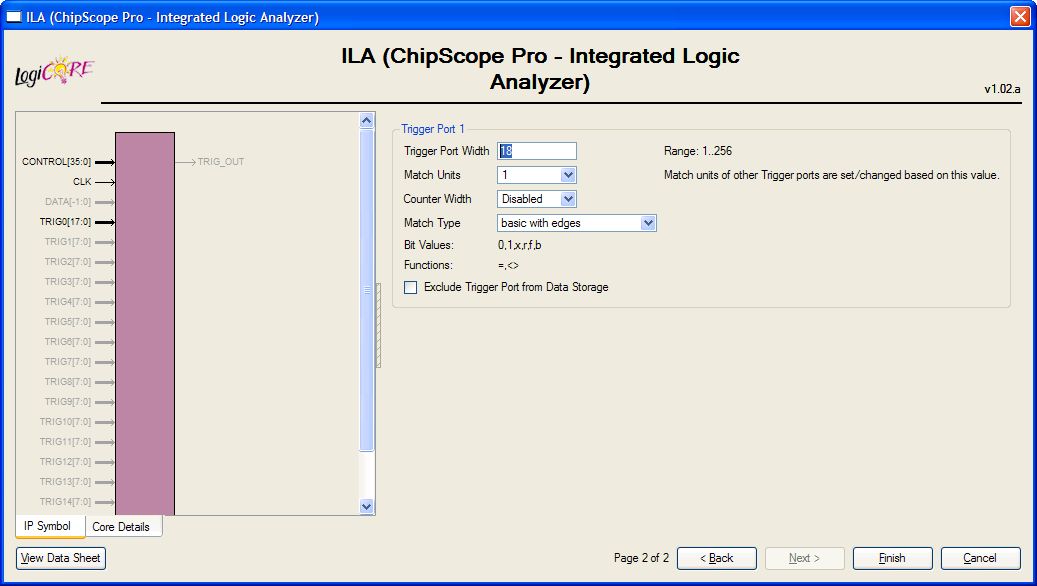

W Coregenerator wybrać blok Debug&Verification/ChipscopePro/ILA (w najnowszej wersji)

oraz nadać mu następujące parametry:

Rys. 5 Parametry bloku ILA

-

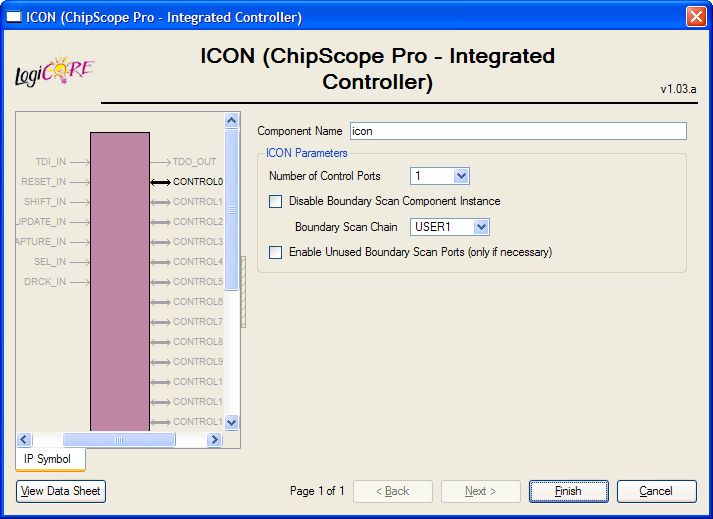

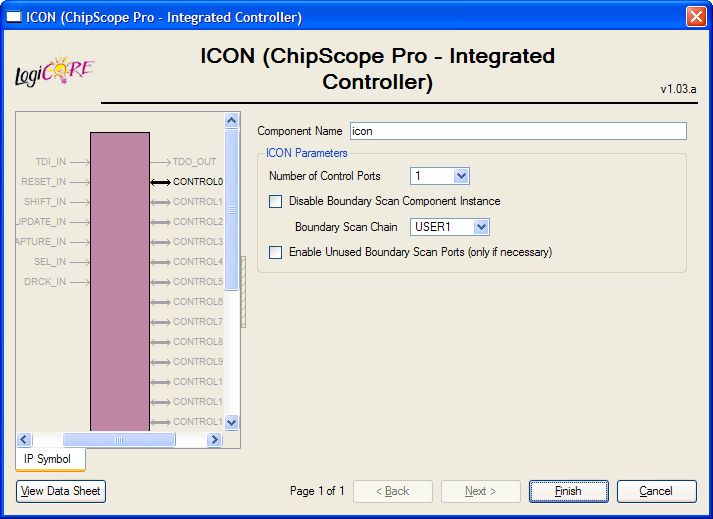

Następnie dodać blok chipscope_icon, również korzystając z programu Coregenerator,

wybierając Debug&Verification/ChipscopePro/ICON (w najnowszej wersji):

Rys. 6 Parametry bloku ICON

-

Dodać do projektu wygenerowane bloki, korzystając ze schematu blokowego z rys. 7 i deklaracji komponentów:

component icon

PORT (

CONTROL0 : INOUT STD_LOGIC_VECTOR(35 DOWNTO 0));

end component;

component ila

PORT (

CONTROL : INOUT STD_LOGIC_VECTOR(35 DOWNTO 0);

CLK : IN STD_LOGIC;

TRIG0 : IN STD_LOGIC_VECTOR(17 DOWNTO 0));

end component;

Należy obserwować sygnały data_i, data_o, err_o i rst_i.

Zwiększyć częstotliwość zegara clk do maksymalnej.

Rys. 7 Schemat podłączenia analizatora Chipscope do układu

Praca z analizatorem Chipscope

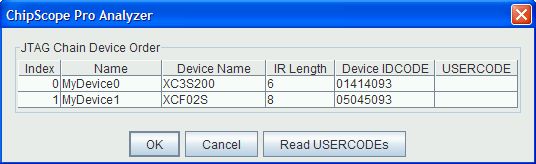

Po implementacji układu z wbudowanymi blokami ILA i ICON, można się podłączyć do

wbudowanego w FPGA analizatora za pomocą programu Chipscope Pro Analyzer.

Po uruchomieniu programu i naciśnięciu przycisku  ,

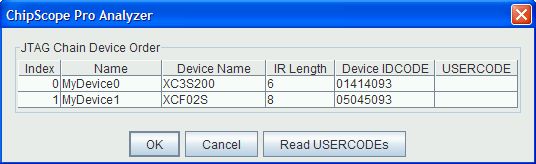

powinno się pojawić okienko pokazujące wykryty łańcuch JTAG (rys.8).

Klikamy OK.

,

powinno się pojawić okienko pokazujące wykryty łańcuch JTAG (rys.8).

Klikamy OK.

Rys. 8 Wykryte układy w łańcuchu JTAG

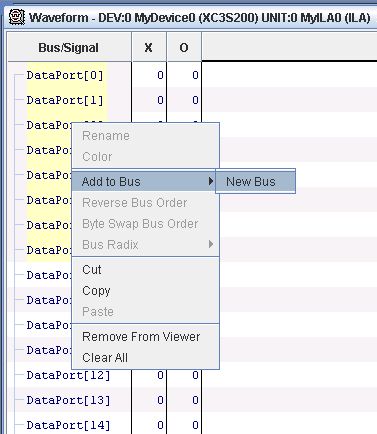

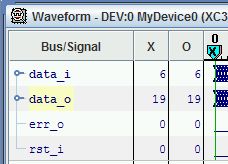

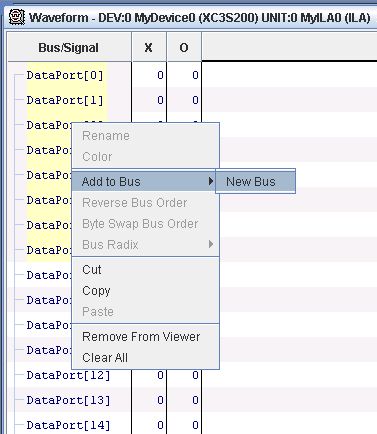

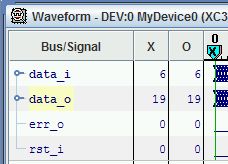

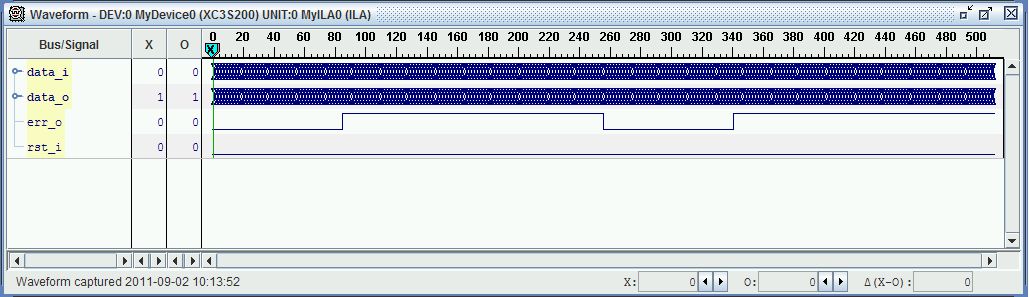

Najpierw należy pogrupować obserwowane sygnały w magistrale (rys.9) i nadać im nazwy, jak na rys.10

(klikamy prawym przycikiem myszy na magistralę i wybieramy Rename).

W tym przypadku dobrze jest ustawić sposób wyświetlania danych wejściowych i wyjściowych (Bus Radix)

z układu DUT jako Unsigned Decimal.

Rys. 9 Grupowanie sygnałów w magistralę.

Rys. 10 Sygnały z odpowiednio nadanymi nazwami.

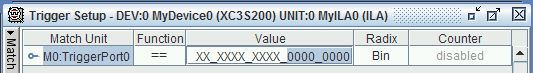

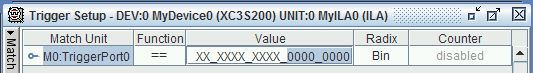

Następnie ustawiamy wyzwalanie analizatora (tj. początek rejestracji danych).

Najlepiej rejestrować dane od początku, tj. gdy data_i=0. Na rys. 11 pokazano

ustawienie układu wyzwalania. UWAGA: zera należy wpisać w miejsca odpowiadające

sygnałom data_i. W Twoim projekcie może to wyglądać inaczej!

Rys. 11 Ustawienie wyzwalania.

Uruchamiamy analizator: Trigger Setup/Run  .

Jeśli ustawiony warunek wyzwalania jest wykryty wewnątrz układu, to nastąpi wyświetlenie danych.

.

Jeśli ustawiony warunek wyzwalania jest wykryty wewnątrz układu, to nastąpi wyświetlenie danych.

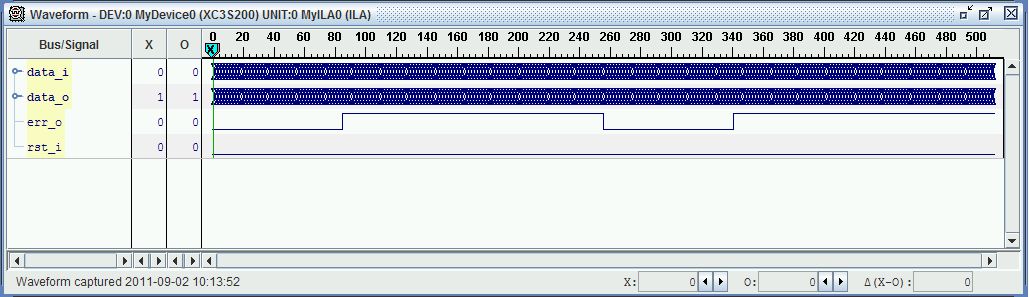

Rys. 12 Widok sygnałów odczytanych przez analizator Chipscope.

Wskaźnik  pokazuje moment wyzwolenia.

pokazuje moment wyzwolenia.

Początek wyświetlania danych można zmieniać zmienić w oknie Capture/Position.

Aby pobrać dane bez czekania na wyzwolenie: Trigger Setup/Trigger Immediate  .

.

Plik ucf do zadania, płytka Digilent Spartan-3, układ Spartan-3 3S200 FT256-4:

#########################################################################################

# Clock:

NET "clk_i" LOC = "T9" ; # 50 MHz clock

#########################################################################################

# Push-buttons:

NET "rst_i" LOC = "L14" ; # pressed high BTN3

#########################################################################################

# LEDs:

NET "leds_o<0>" LOC = "K12" ; # high on

NET "leds_o<1>" LOC = "P14" ; # high on

NET "leds_o<2>" LOC = "L12" ; # high on

NET "leds_o<3>" LOC = "N14" ; # high on

NET "leds_o<4>" LOC = "P13" ; # high on

NET "leds_o<5>" LOC = "N12" ; # high on

NET "leds_o<6>" LOC = "P12" ; # high on

NET "leds_o<7>" LOC = "P11" ; # high on

#########################################################################################

# Seven-segment LED display:

NET "led7_an_o<3>" LOC = "E13" ; # leftmost digit, active low

NET "led7_an_o<2>" LOC = "F14" ; # active low

NET "led7_an_o<1>" LOC = "G14" ; # active low

NET "led7_an_o<0>" LOC = "d14" ; # rightmost digit, active low

#

NET "led7_seg_o<7>" LOC = "E14" ; # segment 'A', active low

NET "led7_seg_o<6>" LOC = "G13" ; # segment 'B', active low

NET "led7_seg_o<5>" LOC = "N15" ; # segment 'C', active low

NET "led7_seg_o<4>" LOC = "P15" ; # segment 'D', active low

NET "led7_seg_o<3>" LOC = "R16" ; # segment 'E', active low

NET "led7_seg_o<2>" LOC = "F13" ; # segment 'F', active low

NET "led7_seg_o<1>" LOC = "N16" ; # segment 'G', active low

NET "led7_seg_o<0>" LOC = "P16" ; # segment 'dp', active low

#########################################################################################

należy odpowiednio dodać do projektu. Aby to zrobić, należy:

należy odpowiednio dodać do projektu. Aby to zrobić, należy:

,

powinno się pojawić okienko pokazujące wykryty łańcuch JTAG (rys.8).

Klikamy OK.

,

powinno się pojawić okienko pokazujące wykryty łańcuch JTAG (rys.8).

Klikamy OK.

.

Jeśli ustawiony warunek wyzwalania jest wykryty wewnątrz układu, to nastąpi wyświetlenie danych.

.

Jeśli ustawiony warunek wyzwalania jest wykryty wewnątrz układu, to nastąpi wyświetlenie danych.

pokazuje moment wyzwolenia.

pokazuje moment wyzwolenia. .

.