Kaskodowy wzmacniacz operacyjny CMOS

badania symulacyjne i projekt topografii

Zadanie 2 składa się z dwóch części:

· badań symulacyjnych kaskodowego wzmacniacza operacyjnego,

· zaprojektowania topografii wzmacniacza, ekstrakcji schematu z projektu topografii i weryfikacji jego parametrów.

Przed przystąpieniem do wykonania zadania należy powtórzyć wiadomości na temat wzmacniaczy operacyjnych oraz obsługi symulatora PSPICE i edytora topografii MAGIC.

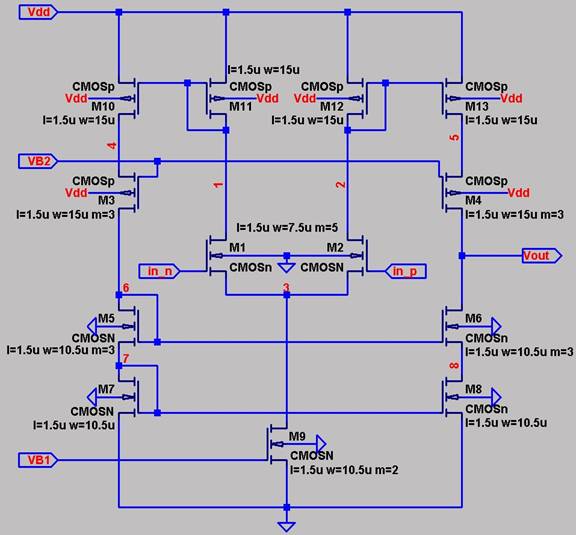

Na rysunku 1 przedstawiono schemat operacyjnego wzmacniacza kaskodowego zaprojektowanego dla technologii AMI 0,5um. Napięcie zasilające Vdd wzmacniacza wynosi 3,3V, a wejściowe napięcie sumacyjne wynosi Vdd/2. Napięcie polaryzujące VB1 należy dobrać tak, aby prąd polaryzujący parę różnicową (IDM9) wynosił 10uA - parzyste nr indeksu i 20uA- nieparzyste numery indeksu, natomiast napięcie polaryzujące VB2 dobrać tak, aby uzyskać jak największy zakres zmian napięcia wyjściowego. Dobór napięcia proszę uzasadnić w sprawozdaniu. Należy również zaproponować i wykonać modyfikację schematu wzmacniacza poprawiającą zakres zmian napięcia wyjściowego.

W pierwszej części zadania na podstawie symulacji wzmacniacza obciążonego CL=4pF należy wyznaczyć:

· punkty pracy tranzystorów i moc strat Pdiss wzmacniacza,

· napięcie niezrównoważenia wzmacniacza,

· charakterystyki wzmocnienia napięciowego w otwartej pętli sprzężenia zwrotnego, odczytać Avo, GB, PM,

· zakres zmian wejściowego napięcia sumacyjnego ICMR,

· zakres zmian napięcia wyjściowego Voutswing,

· szybkość zmian napięcia wyjściowego,

· współczynniki CMRR i PSRR,

· pojemność wejściową Cin, rezystancję wyjściową Rout.

Dodatkowo, stosując analizę Monte Carlo, należy zbadać wpływ rozrzutu względnego parametrów tranzystorów na wejściowe napięcie niezrównoważenia Vioff, wzmocnienie stałoprądowe Avo wzmacniacza i CMRR. W tym celu przyjąć, że tranzystory MOS mają 0.5% rozrzutu napięcia progowego oraz współczynnika transkonduktancji (w modelach tranzystorów MOS po VTH0 i TOX dodać parametr DEV=0.5%)

Rys. 1 Schemat wzmacniacza kaskodowego

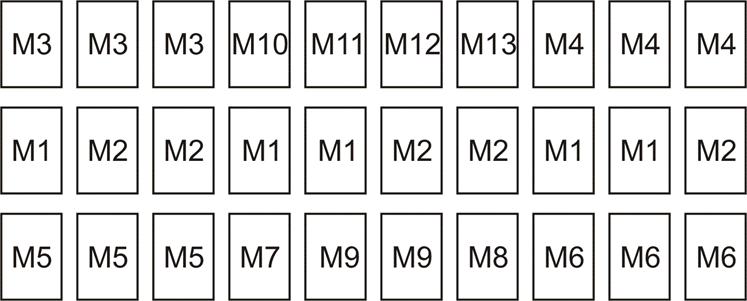

W drugiej części zadania należy wykonać projekt topografii wzmacniacza przy użyciu programu MAGIC stosując następujące rozmieszczenie tranzystorów:

Rys. 1 Rozmieszczenie tranzystorów wzmacniacza kaskodowego

Następnie z projektu topografii należy wykonać ekstrakcję schematu wzmacniacza i przeprowadzić badania symulacyjne.

Do zadania należy sporządzić sprawozdanie w formacie doc, odt lub pdf według załączonego wzoru. Sprawozdanie powinno zawierać zestawienia wyznaczonych parametrów w tabeli oraz odpowiednie wykresy, obliczenia i wnioski. Do sprawozdana należy dołączyć pliki do symulatora SPICE (cir lub asc) i projekty topografii (mag). UWAGA! Do każdej symulacji należy załączyć odpowiedni plik gotowy do uruchomienia! Spakowane zipem sprawozdanie wraz załączonymi plikami należy przesłać do serwisu eNauczanie. Dodatkowo należy przesłać sprawozdanie w formacie pdf. Przesyłane pliki należy nazywać według szablonu: Imię_Nazwisko_numerindeksu_AUSLAB_rok_zad2.