Wyświetlanie bitmapy na ekranie

VGA

Treść zadania

(przystosowana do laboratorium zdalnego):

Należy zaprojektować moduł generujący sygnały VGA. Działanie

modułu powinno być następujące:

- należy generować następujące sygnały:

czterobitowe sygnały kolorów R (red_o), G (green_o), B (blue_o),

synchronizację pionową (vsync_o) i poziomą (hsync_o);

- sygnały należy generować zgodnie z normą dla

standardu VGA 60Hz, 640x480 pikseli;

- na ekranie VGA powinno być widoczne tło o

kolorze wybieranym trzema przełącznikami na płytce FPGA, każdy z

przełączników powinien włączać pojedynczy kolor tj. SW5 powinien włączać

kolor czerwony, SW6 kolor zielony oraz SW7 kolor niebieski;

- na ekranie powinien być wydzielony prostokąt o

wymiarach 256 x 96 pikseli;

- w prostokącie opisanym powyżej powinien być

wyświetlany obraz pobierany z synchronicznej pamięci ROM, w której

zapisany jest plik graficzny typu BMP;

- prostokąt z bitmapą powinien być ruchomy, jego

położenie na ekranie powinno być zmieniane za pomocą przycisków: BTN0 –

przesunięcie w lewo, BTN1 – przesunięcie w dół, BTN2 – przesunięcie w

górę, BTN3 – przesunięcie w prawo; dla ułatwienia: przesuwanie bitmapy

powinno odbywać się z prędkością 60 pikseli / sek (wystarczy sprawdzać

stan przycisków podczas synchronizacji pionowej i realizować przesunięcie

o jeden piksel).

- przesuwanie prostokąta z bitmapą powinno być

ograniczone do brzegów ekranu (prostokąt nie może wyjechać poza ekran);

- wspomnianą powyżej pamięć ROM należy wygenerować

za pomocą generatora IP core dostępnego poprzez IP Catalog w Vivado –

instrukcja poniżej;

- sygnał zegarowy (clk_i) ma częstotliwość 100

MHz;

- nie używamy sygnału „reset”, proszę korzystać z

wartości początkowych sygnałów i zmiennych.

Rys. 1 Obrazek do wyświetlenia na monitorze VGA.

Wymagania dotyczące zaliczenia:

Symulacja funkcjonalna nie jest obowiązkowa (ale może być wykonana w razie

konieczności).

Należy zaprogramować płytkę testową FPGA i praktycznie sprawdzić

działanie układu (przebieg testu przedstawić na filmie):

- Zademonstrować

przesuwanie prostokąta z bitmapą w lewo, w prawo, w górę i w dół (za

każdym razem dojechać do krawędzi ekranu, aby pokazać czy prostokąt się

prawidłowo zatrzymuje). Proszę wykonać to zadanie tak, aby nie „wjeżdżać”

pod obszar zasłonięty płytką FPGA.

- Ustawić

prostokąt z bitmapą tak, aby był cały widoczny (aby nie zasłaniała go

płytka leżąca na monitorze).

- Przełączyć

kolory tła za pomocą przełączników SW5, SW6, SW7 kolejno na: czerwony,

żółty, zielony, cyjan, niebieski, magenta, biały, a następnie wrócić do

czarnego.

Uwagi i informacje dodatkowe:

Wejścia i wyjścia układu:

clk_i – zegar 100MHz,

red_o – wyjście sygnału

koloru czerwonego do monitora (4 bity),

green_o – wyjście sygnału

koloru zielonego do monitora (4 bity),

blue_o – wyjście sygnału

koloru niebieskiego do monitora (4 bity),

hsync_o – wyjście sygnału

synchronizacji poziomej do monitora,

vsync_o – wyjście sygnału

synchronizacji pionowej do monitora,

sw5_i – przełącznik do

ustawiania czerwonej składowej tła,

sw6_i – przełącznik do ustawiania

zielonej składowej tła,

sw7_i – przełącznik do

ustawiania niebieskiej składowej tła,

btn_i – przyciski do

przesuwania prostokąta z bitmapą (4 bity).

Plik z ograniczeniami

projektowymi: iup10.xdc

Obrazek do wyświetlania w

formacie COE

oraz BMP.

Informacje o analogowym

sygnale VGA (częstotliwość pikseli można ustalić na równe 25 MHz):

Generowanie

sygnału VGA

Parametry sygnału VGA

Przy generacji sygnału wideo należy pamiętać o

zerowaniu sygnałów RGB poza obszarem wyświetlania obrazu VGA (na podstawie

poziomu sygnału analogowego poza obszarem wyświetlania monitor ustala poziom

czerni dla każdego z kolorów).

Sygnały red_o, green_o i

blue_o są czterobitowe, ale wszystkie bity poszczególnych sygnałów sterujemy

równocześnie tą samą wartością (mamy więc 8 możliwych kolorów), np.:

red_o <= red & red

& red & red; -- lokalny sygnał

red jest typu std_logic

Monitor po wykryciu sygnału

video włącza się z uśpienia, pełną jasność ekranu osiągnie po około 1 minucie.

Instrukcja syntezy modułu pamięci ROM za pomocą generatora IP core w

Vivado:

·

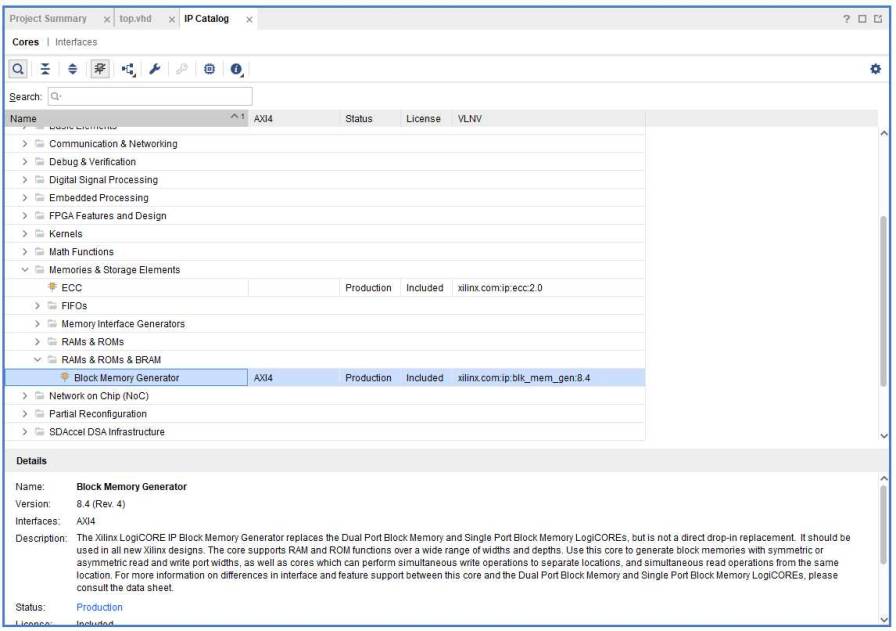

W okienku Flow

navigator rozwijamy PROJECT MANAGER i klikamy w IP Catalog.

·

Następnie rozwijamy Memories

& Storage Elements i dalej rozwijamy RAMs & ROMs & BRAM.

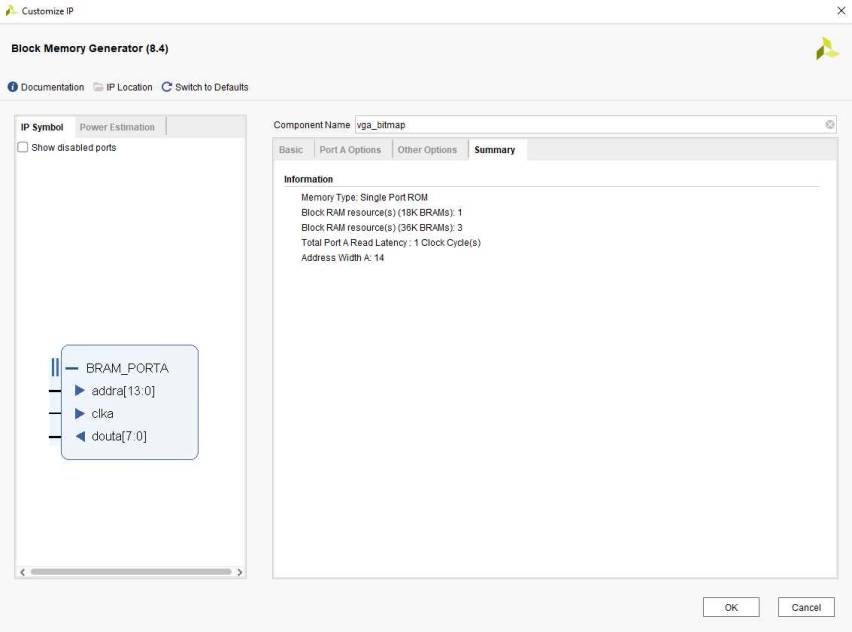

Poniżej przedstawiono omawiane okno dialogowe.

·

Klikamy podwójnie w Block

Memory Generator.

·

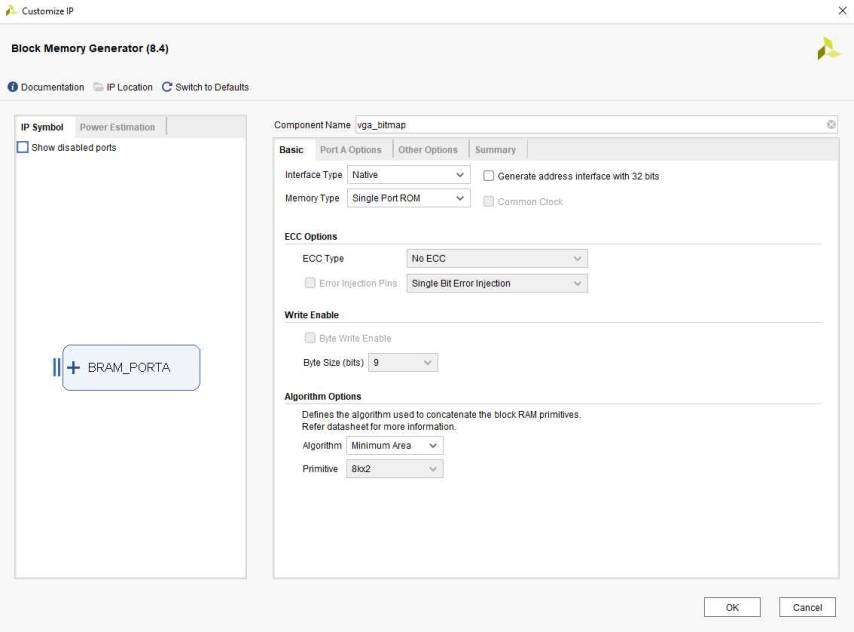

W polu Component

Name wpisujemy nazwę, którą otrzyma generowany przez nas moduł, np.: vga_bitmap

·

W zakładce Basic

zmieniamy Memory Type na Single Port ROM. Poniżej przedstawiono

omawiane okno dialogowe.

·

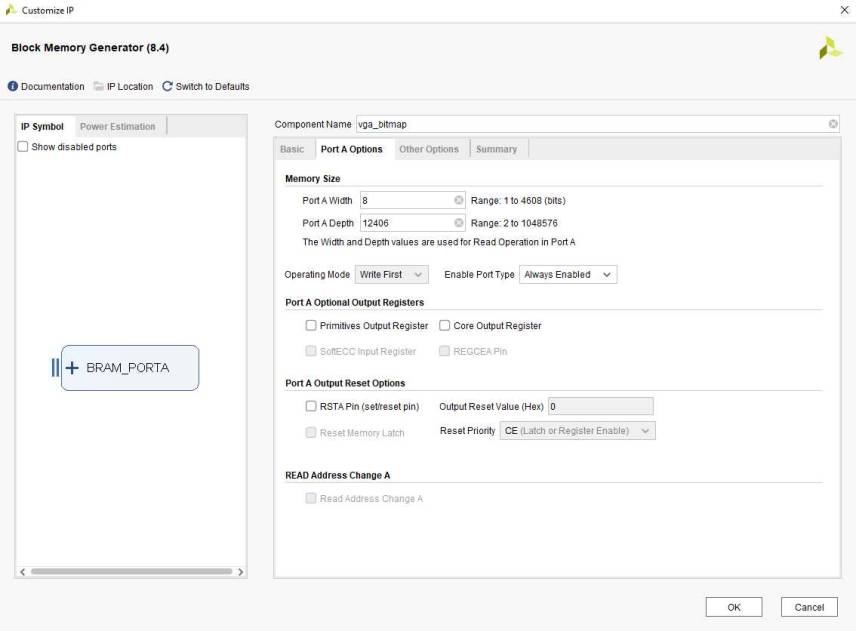

W zakładce Port A

Options zmieniamy Port A Width na 8, następnie zmieniamy Port

A Depth na 12406, następnie w polu Enable Port Type wybieramy

Always Enabled.

Wyłączamy opcję Primitives Output Register.

Poniżej przedstawiono omawiane okno dialogowe.

·

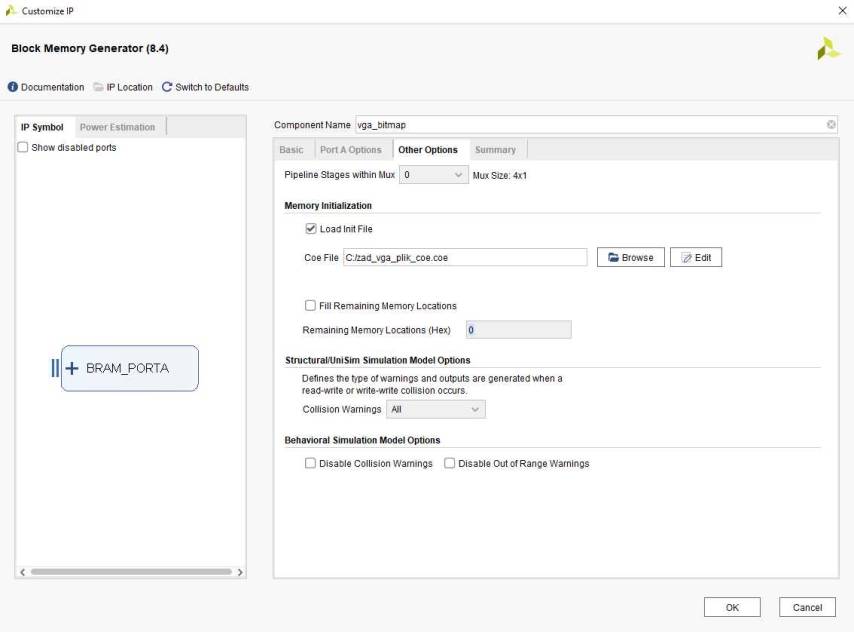

W zakładce Other

Options zaznaczamy Load Init File, a następnie za pomocą przycisku Browse

znajdujemy plik zad_vga_plik_coe.coe

zawierający plik bitmapy i klikamy w OK. Pliku nie edytujemy.

Poniżej przedstawiono omawiane okno dialogowe.

·

Znajdujący się w lewym

górnym rogu przycisk Documentation otworzy szczegółową dokumentację

generowanego komponentu.

·

W zakładce Summary

możemy znaleźć podsumowanie istotnych parametrów tworzonego komponentu.

Szczególnie istotna jest informacja: Total Port A Read Latency: 1 Clock

Cycle(s). Oznacza ona, że odczyt z pamięci odbywa się z opóźnieniem 1 cyklu

zegara w stosunku do zbocza zegarowego zatrzaskującego odczytywany adres. W

przypadku wątpliwości proszę zajrzeć do dokumentacji komponentu.

Poniżej przedstawiono omawiane okno dialogowe.

·

Na zakończenie

potwierdzamy ustawienia przyciskiem OK w prawym dolnym rogu i po chwili

zatwierdzamy w okienku Generate Output Products przyciskiem Generate rozpoczęcie

syntezy nowego komponentu.

·

Jeszcze raz

potwierdzamy w okienku Generate Output Products przyciskiem OK.

·

Po zakończeniu

generacji komponent zostanie dołączony do listy plików źródłowych projektu.

W celu ułatwienia dołączenia komponentu do

hierarchii aktualnego projektu w okienku Sources można wybrać zakładkę IP

sources. Wtedy wyświetlą się wygenerowane moduły IP. Po rozwinięciu

wybranego modułu oraz rozwinięciu Instantiation Template można zobaczyć

plik *.vho zawierający szkielet deklaracji komponentu oraz przykład jego

użycia (tworzenia instancji). Możemy te elementy łatwo przekopiować do naszego

pliku projektowego, w którym planujemy podłączyć wygenerowany komponent, a

zaprojektowany komponent zajmie właściwe miejsce w hierarchii projektu.

Istotny fragment przykładowego pliku VHO:

--

The following code must appear in the VHDL architecture header:

------------- Begin Cut here for COMPONENT Declaration ------ COMP_TAG

component vga_bitmap

port (

clka: IN std_logic;

addra: IN std_logic_VECTOR(13

downto 0);

douta: OUT std_logic_VECTOR(7

downto 0));

end component;

-- COMP_TAG_END ------ End COMPONENT Declaration ------------

-- The following code must appear in the VHDL architecture

-- body. Substitute your own instance name and net names.

------------- Begin Cut here for INSTANTIATION Template ----- INST_TAG

your_instance_name : vga_bitmap

port map (

clka => clka,

addra => addra,

douta => douta);

-- INST_TAG_END ------ End INSTANTIATION Template ------------

-- You must compile the wrapper file vga_bitmap.vhd when simulating

-- the core, vga_bitmap. When compiling the wrapper file, be sure to

-- reference the VHDL simulation library.

Tekst zaznaczony na czerwono należy skopiować do obszaru definicji

sygnałów lokalnych. Tekst zaznaczony na niebiesko

(po ustaleniu nazwy instancji komponentu oraz sygnałów podłączonych) należy

skopiować do obszaru opisu systemu. Po dokonaniu powyższych modyfikacji

komponent powinien zająć właściwe miejsce w hierarchii plików projektu.