Symulacja funkcjonalna projektu

Najpierw należy utworzyć plik z testujący (testbench) dla testowanego układu. Pisząc testbench w języku VHDL lub Verilog – po prostu tworzymy nowy moduł/entity w języku HDL (bez portów – są nie potrzebne), nazywamy go np. testbench, a następnie osadzamy w nim symulowany układ. W pliku testbench za pomocą języka HDL generujemy także sygnały pobudzające.

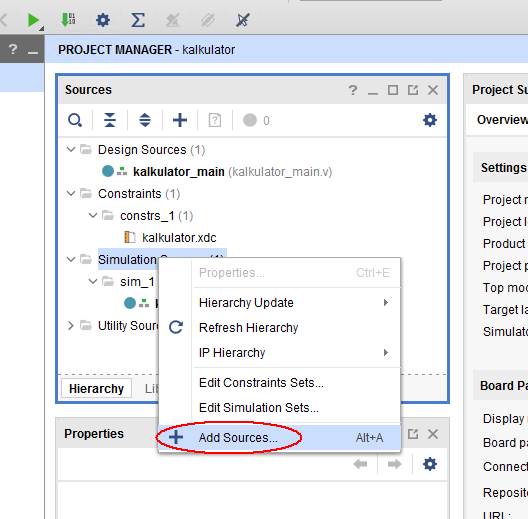

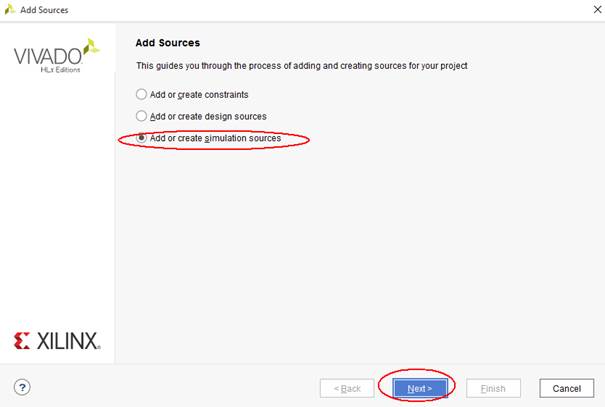

1. Dodajemy nowy plik testbench do projektu:

i wybieramy Add or create simulation sources:

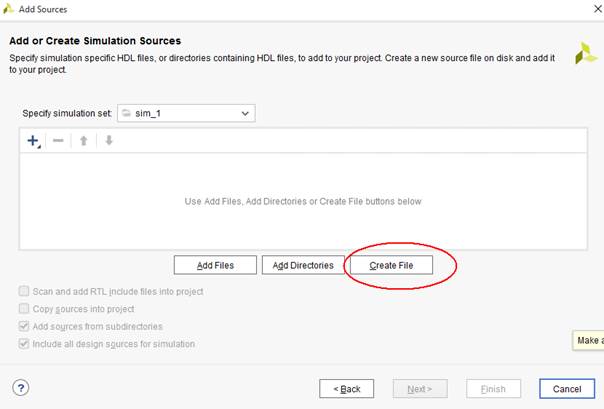

2. W następnym oknie wybieramy Create File:

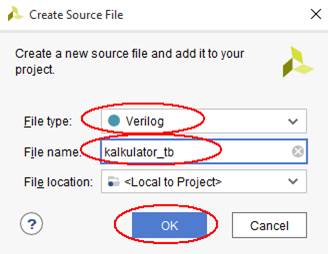

i podajemy typ pliku (Verilog lub VHDL) oraz jego nazwę:

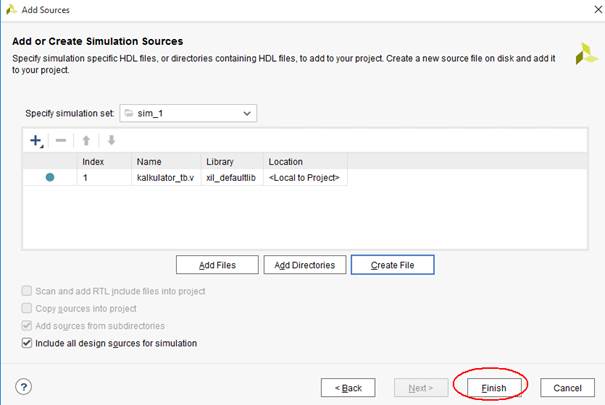

3. Na koniec naciskamy Finish:

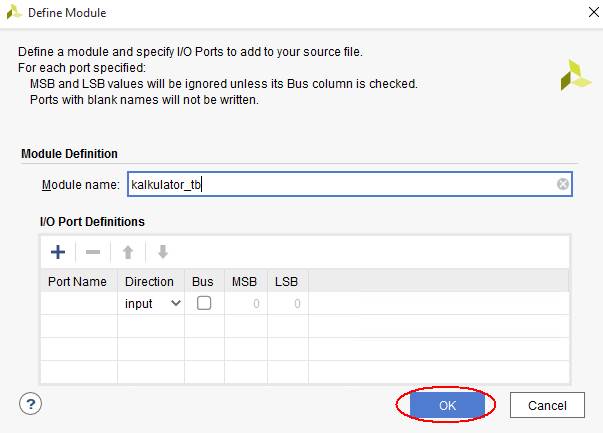

4. System zapyta jeszcze, czy chcemy wprowadzić porty. Testbench nie musi posiadać portów, więc klikamy OK i potwierdzamy Yes:

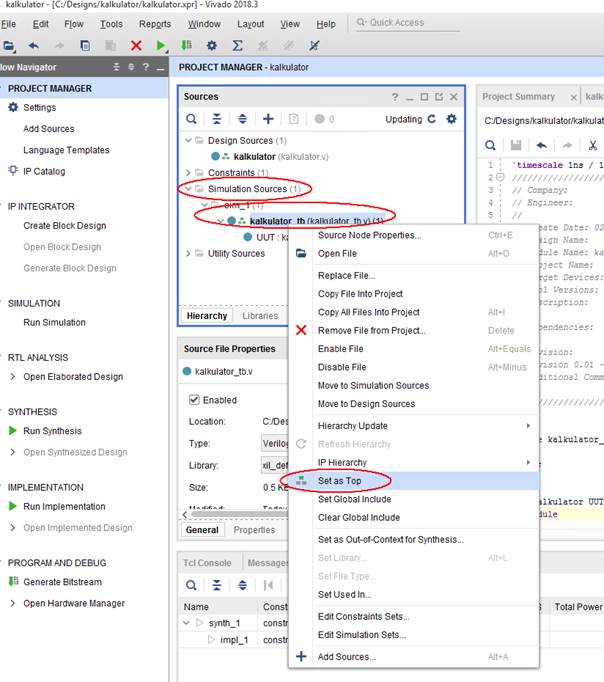

5. Po poprawnym napisaniu plików HDL, w projekcie powinniśmy zobaczyć prawidłową strukturę naszego kodu.

Do symulacji plik testbench powinien być wybrany jako "top", jego nazwa w hierarchii projektu powinna być wypisana pogrubioną czcionką. Zawsze możemy wybrać plik top naciskając na danym pliku prawym przyciskiem myszy:

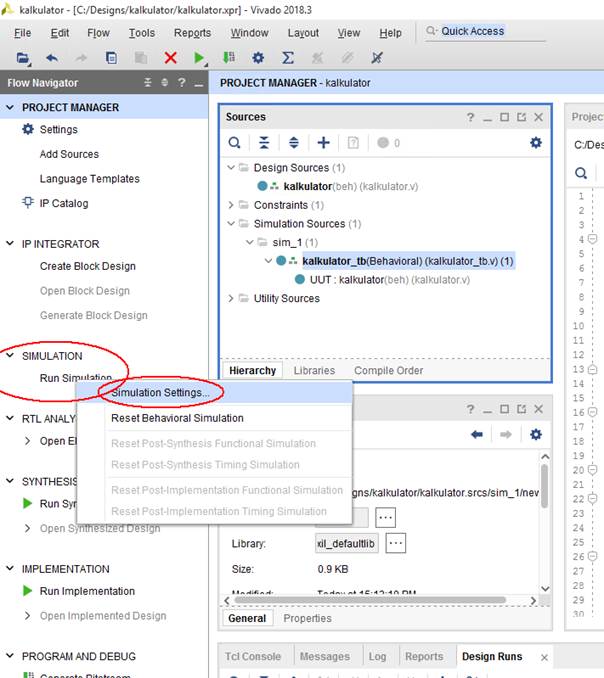

6. W pliku testbench powinny się znajdować pobudzenia. Przed uruchomieniem symulacji dobrze jest ustawić czas trwania symulacji, klikając prawym przyciskiem myszy na SIMULATION i wybierając Simulation Settings:

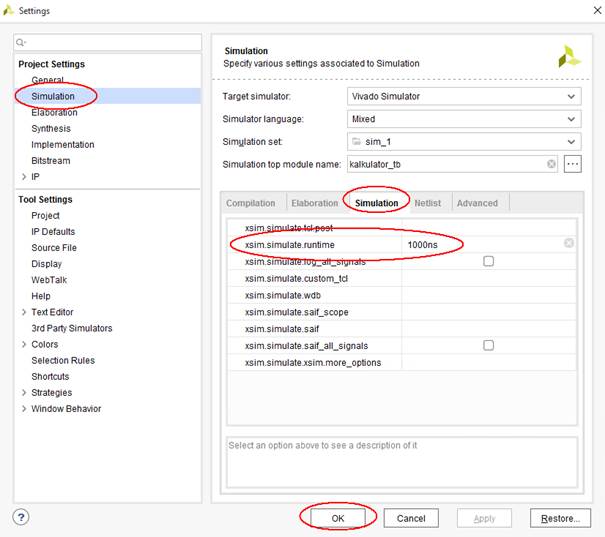

7. Następnie w zakładce Simulation wprowadzamy, do kiedy ma trwać symulacja:

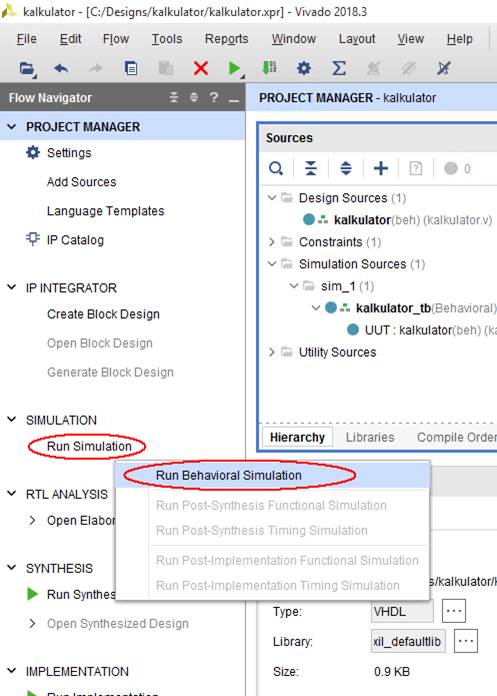

8. Teraz można uruchomić symulację funkcjonalną: SIMULATION/Run Simulation/Run Behavioral Simulation:

Symulacja funkcjonalna (Behavioral) to symulacja samego kodu HDL, bez uwzględnienia np. opóźnień wynikających z połączeń w układzie FPGA oraz opóźnień rzeczywistych elementów cyfrowych. Jeśli wykonamy syntezę i implementację, to po każdym etapie można również wykonać inne symulacje, która będą uwzględniały więcej czynników związanych z syntezą i implementacją.

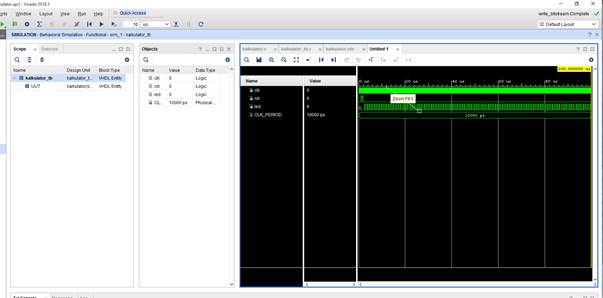

9. Po wykonaniu symulacji, system przełączy się w tryb wyświetlania symulacji:

Wykonując gesty myszką, można zmienić widok, np.

· przeciągając w lewo i w górę = powiększamy

· przeciągając w prawo i górę = pomniejszamy.

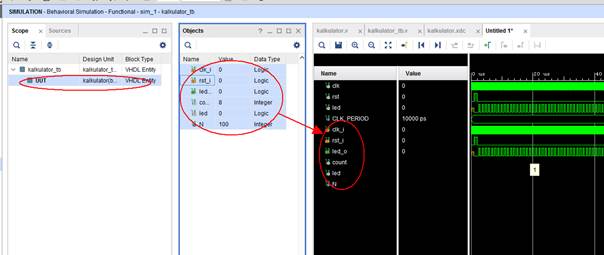

Możemy też dodać sygnały z innych modułów projektu: należy wybrać moduł i przeciągnąć sygnały myszką:

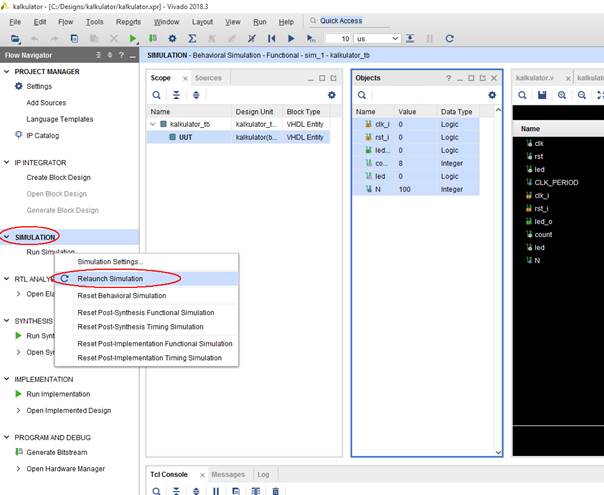

10. Po dodaniu nowych sygnałów, przeważnie trzeba ponownie uruchomić symulację (Relaunch Simulation):