Design simulation

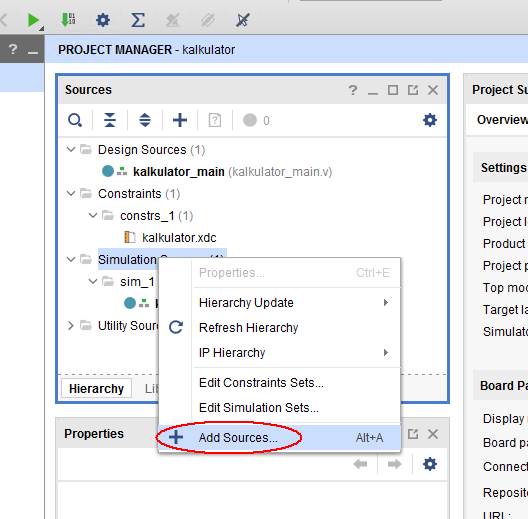

1. Add new testbench file to the project:

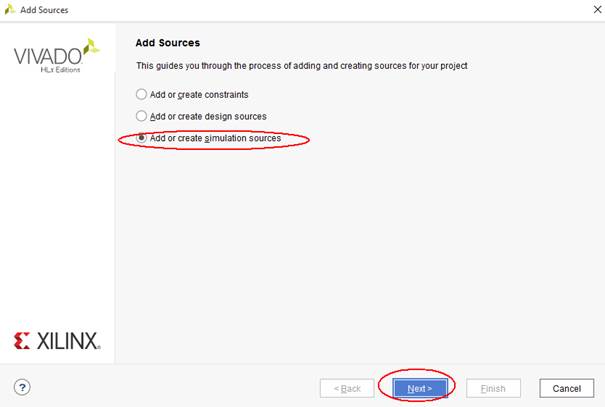

and select Add or create simulation sources:

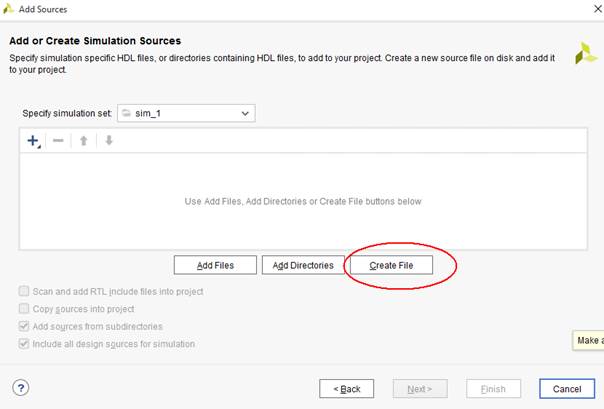

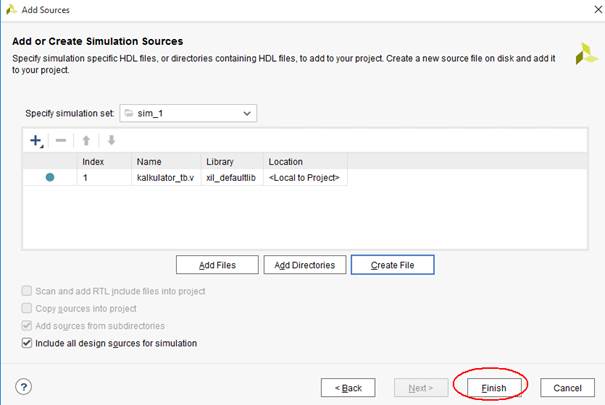

2. In the next windows, select Create File:

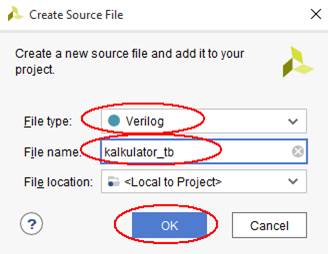

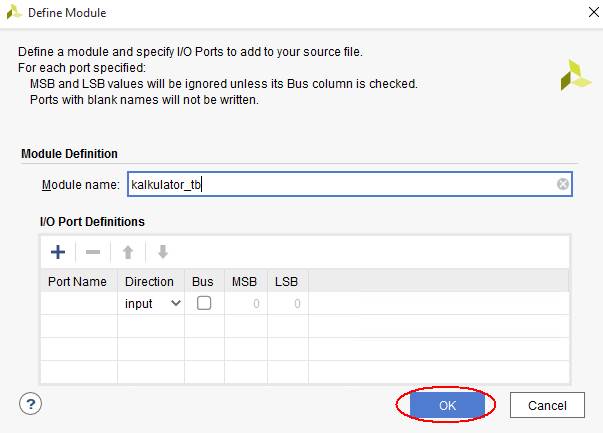

then enter the file type (Verilog lub VHDL) and its name:

3. At the end select Finish:

4. The system will ask if we want to enter ports. Testbench does not need to have ports, so click OK and confirm Yes:

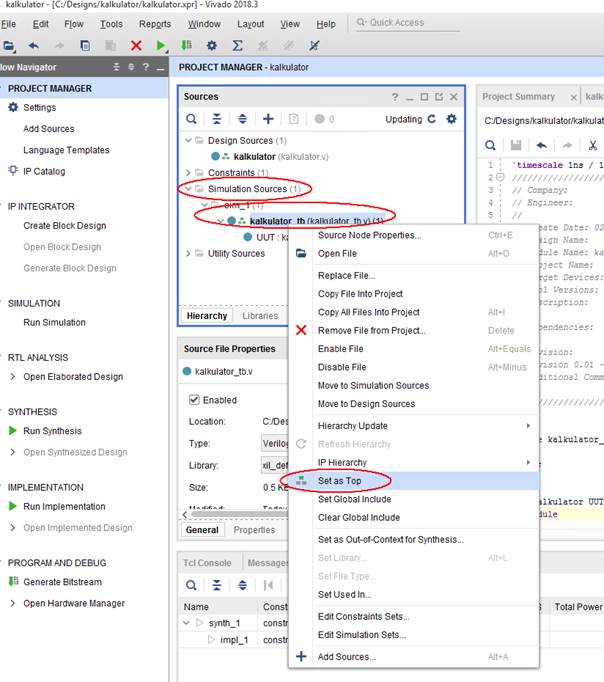

5. After correctly writing HDL files, in the project we should see the correct structure of our code.

For simulation, the testbench file should be selected as "top", its name in the project hierarchy should be in bold type. We can always select the top file by right-clicking on the given file:

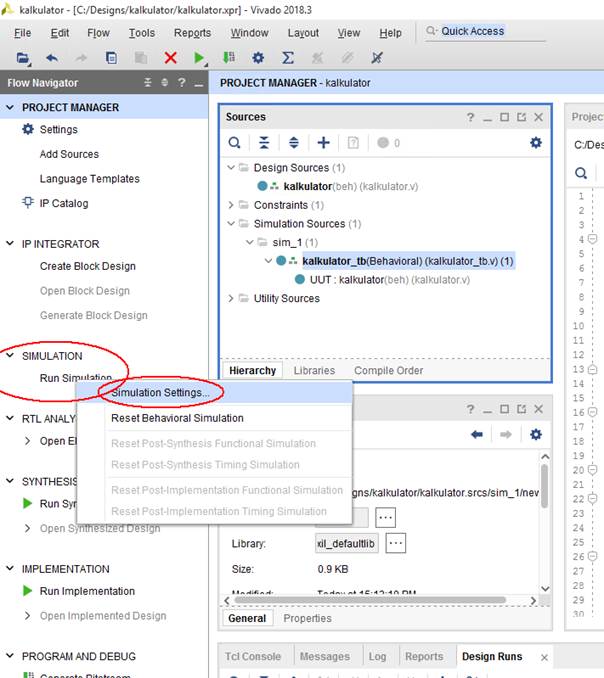

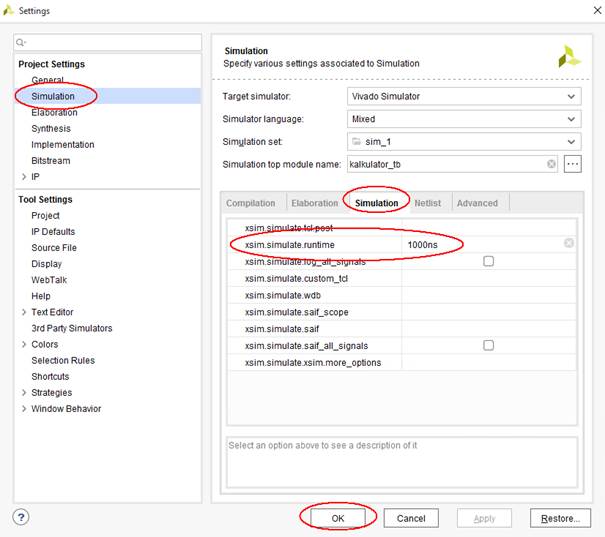

6. The testbench file should contain the stimulus. Before running the simulation, it is a good idea to set the duration of the simulation by right-clicking on SIMULATION and selecting Simulation Settings:

7. Then, in the Simulation tab, enter how long the simulation should run:

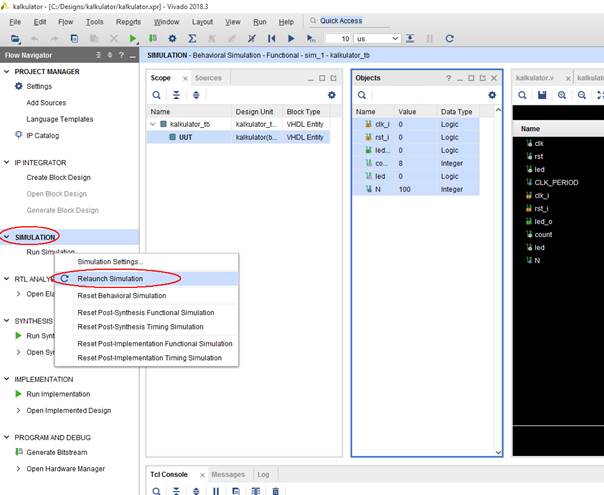

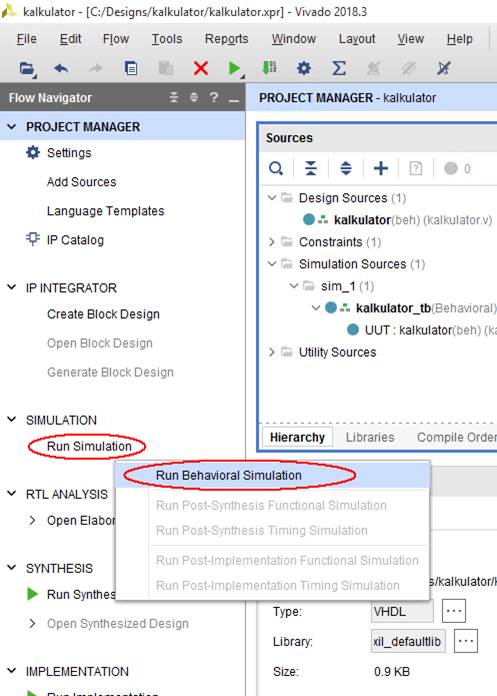

8. Now you can start the functional siumulation: SIMULATION/Run Simulation/Run Behavioral Simulation:

Functional simulation (Behavioral) is a simulation of the HDL code itself, without taking into account, for example, delays resulting from connections in the FPGA system and delays of real digital elements. If we perform a synthesis and implementation, then after each stage other simulations can also be made, which will take into account more factors related to the synthesis and implementation.

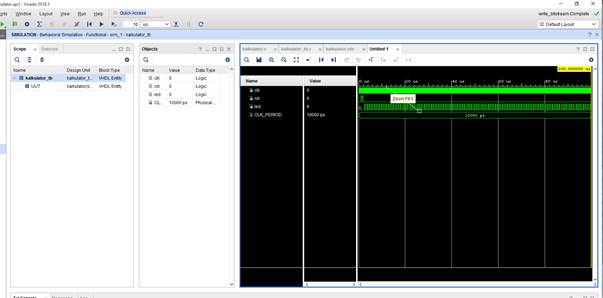

9. After the simulation is completed, the system will switch to the simulation display mode:

By making mouse gestures, you can change the view, e.g.

- By dragging left and up = we enlarge

- Dragging to the right and up = zoom out.

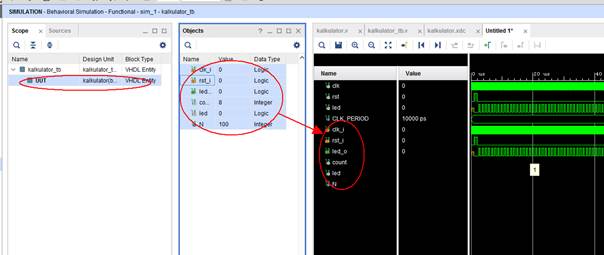

We can also add signals from other project modules: select a module and drag the signals with the mouse:

10. After adding new signals, you usually need to restart the simulation (Relaunch Simulation):