Generator parzystości

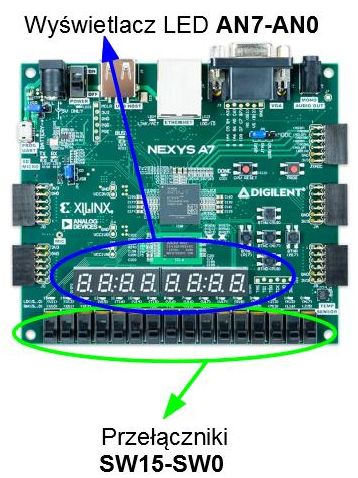

Zadanie: Należy zaprojektować układ generujący bit parzystości słowa 8-bitowego. Słowo bitowe podawać poprzez przełączniki SW15-SW0 znajdujące się na płytce prototypowej. Parzystość wyświetlać na wyświetlaczu LED: E - parzysta liczba "jedynek" w 8-bitowym słowie wejściowym (ang. even), O - nieparzysta liczba jedynek (ang. odd).

Zadania do wykonania:

- opisać układ za pomocą języka HDL,

- napisać testbench i wykonać symulację funkcjonalną,

- opisać ograniczenia (constraints) w formacie XDC,

- wykonać praktyczną realizację poprzez zaprogramowanie płytki testowej.

Na płytce prototypowej znajduje się 8 wyświetlaczy siedmiosegmentowych o wspólnej anodzie połączonych w sposób multipleksowany. Wynik należy wyświetlić na dowolnym jednym wyświetlaczu. Połączenie multipleksowane jest wykonane poprzez wspólne połączenie wszystkich wyprowadzeń segmentowych tj. połączenie segmentów A w 8 wyświetlaczach, połączenie segmentów B w 8 wyświetlaczach itd. Wspólne anody służą do aktywacji danego znaku. Poszczególne segmenty pojedynczego wyświetlacza uaktywniane są podaniem stanu niskiego na wyprowadzenia A - G. Włączenie poszczególnych wyświetlaczy aktywowane jest stanem niskim na wyprowadzeniach AN7 - AN0 (zanegowana wspólna anoda). Przykładowo, jeśli chcemy wygasić wyświetlacze 0-2 wówczas na wyprowadzenia AN0 - AN2 należy podać '1'. Jeśli równocześnie na wyświetlaczu nr 3 chcemy wyświetlić znak "A", wówczas dodatkowo należy podać następujące sygnały: AN3='0' oraz A='0', B='0', C='0', D='1', E='0', F='0', G='0', DP='1'.

Więcej szczegółów, schematy itp. znajdziesz w instrukcji obsługi płytki Nexys A7, na stronach 22-24.

Plik "constraints" w formacie XDC do zadania, płytka Digilent Nexys A7, układ Artix-7 XC7A100T-1CSG324C (obudowa: CSG324, speed grade:-1):

#########################################################################################

# DIP SW:

set_property -dict { PACKAGE_PIN J15 IOSTANDARD LVCMOS33 } [get_ports sw_i[0] ]

set_property -dict { PACKAGE_PIN L16 IOSTANDARD LVCMOS33 } [get_ports sw_i[1] ]

set_property -dict { PACKAGE_PIN M13 IOSTANDARD LVCMOS33 } [get_ports sw_i[2] ]

set_property -dict { PACKAGE_PIN R15 IOSTANDARD LVCMOS33 } [get_ports sw_i[3] ]

set_property -dict { PACKAGE_PIN R17 IOSTANDARD LVCMOS33 } [get_ports sw_i[4] ]

set_property -dict { PACKAGE_PIN T18 IOSTANDARD LVCMOS33 } [get_ports sw_i[5] ]

set_property -dict { PACKAGE_PIN U18 IOSTANDARD LVCMOS33 } [get_ports sw_i[6] ]

set_property -dict { PACKAGE_PIN R13 IOSTANDARD LVCMOS33 } [get_ports sw_i[7] ]

set_property -dict { PACKAGE_PIN T8 IOSTANDARD LVCMOS33 } [get_ports sw_i[8] ]

set_property -dict { PACKAGE_PIN U8 IOSTANDARD LVCMOS33 } [get_ports sw_i[9] ]

set_property -dict { PACKAGE_PIN R16 IOSTANDARD LVCMOS33 } [get_ports sw_i[10]]

set_property -dict { PACKAGE_PIN T13 IOSTANDARD LVCMOS33 } [get_ports sw_i[11]]

set_property -dict { PACKAGE_PIN H6 IOSTANDARD LVCMOS33 } [get_ports sw_i[12]]

set_property -dict { PACKAGE_PIN U12 IOSTANDARD LVCMOS33 } [get_ports sw_i[13]]

set_property -dict { PACKAGE_PIN U11 IOSTANDARD LVCMOS33 } [get_ports sw_i[14]]

set_property -dict { PACKAGE_PIN V10 IOSTANDARD LVCMOS33 } [get_ports sw_i[15]]

#########################################################################################

#7-SEG LED:

set_property -dict { PACKAGE_PIN J17 IOSTANDARD LVCMOS33 } [get_ports an_o[0]]

set_property -dict { PACKAGE_PIN J18 IOSTANDARD LVCMOS33 } [get_ports an_o[1]]

set_property -dict { PACKAGE_PIN T9 IOSTANDARD LVCMOS33 } [get_ports an_o[2]]

set_property -dict { PACKAGE_PIN J14 IOSTANDARD LVCMOS33 } [get_ports an_o[3]]

set_property -dict { PACKAGE_PIN P14 IOSTANDARD LVCMOS33 } [get_ports an_o[4]]

set_property -dict { PACKAGE_PIN T14 IOSTANDARD LVCMOS33 } [get_ports an_o[5]]

set_property -dict { PACKAGE_PIN K2 IOSTANDARD LVCMOS33 } [get_ports an_o[6]]

set_property -dict { PACKAGE_PIN U13 IOSTANDARD LVCMOS33 } [get_ports an_o[7]]

set_property -dict { PACKAGE_PIN T10 IOSTANDARD LVCMOS33 } [get_ports seg_o[7]]

set_property -dict { PACKAGE_PIN R10 IOSTANDARD LVCMOS33 } [get_ports seg_o[6]]

set_property -dict { PACKAGE_PIN K16 IOSTANDARD LVCMOS33 } [get_ports seg_o[5]]

set_property -dict { PACKAGE_PIN K13 IOSTANDARD LVCMOS33 } [get_ports seg_o[4]]

set_property -dict { PACKAGE_PIN P15 IOSTANDARD LVCMOS33 } [get_ports seg_o[3]]

set_property -dict { PACKAGE_PIN T11 IOSTANDARD LVCMOS33 } [get_ports seg_o[2]]

set_property -dict { PACKAGE_PIN L18 IOSTANDARD LVCMOS33 } [get_ports seg_o[1]]

set_property -dict { PACKAGE_PIN H15 IOSTANDARD LVCMOS33 } [get_ports seg_o[0]]

#########################################################################################