Lab 0: Processor Picoblaze

Introduction

The aim of the exercise is to develop a microelectronic system with a Picoblaze processor, in which the hardware part performs clock frequency division and multiplexed display on an LED display. The tasks of the software include reading the buttons and, depending on this, increasing or decreasing the counter and sending this information to the LED display.

1. Startup version of the system with Picoblaze processor

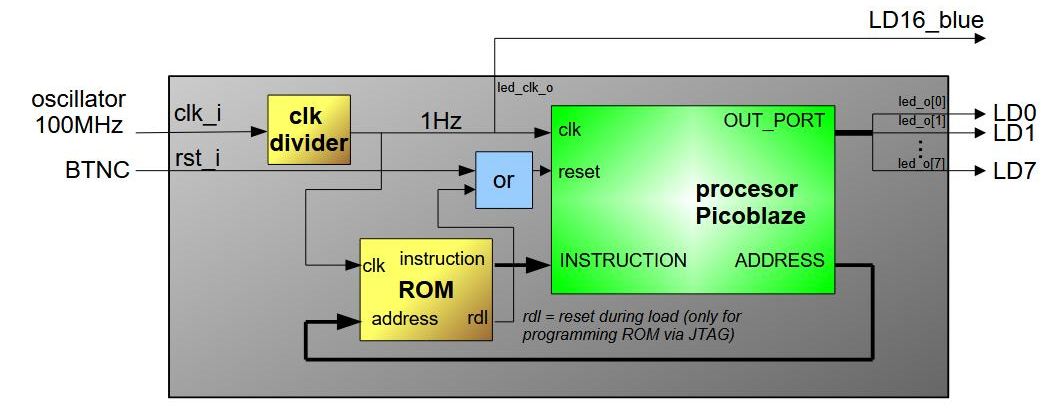

In the first step, a simplified system should be implemented according to the block diagram::

Fig. 1 Block diagram of the startup version of the system.

The clk_i clock from the 100MHz oscillator should be divided to obtain the clk clock for the Picoblaze processor of frequency 1Hz.

Assembly program:

ADDRESS 0 LOAD sA, fE ; write initial value: 11111110 START: OUTPUT sA, 00 ; Write sA to OUT_PORT RL sA ; rotate register sA, i.e. 11111110 -> 11111101 JUMP START ; Jump to beginning (infinite loop)

When embedding a ROM with an assembler program, set the generic parameter indicating that the memory will be implemented in an FPGA from the Virtex-6 family (applies to the Nexys7 board):

C_FAMILY => "V6"

XDC file, Nexys7 board, version for stationary and remote implementation (note: appropriate lines must be deleted!):

#########################################################################################

# CLOCK:

set_property -dict { PACKAGE_PIN E3 IOSTANDARD LVCMOS33 } [get_ports {clk_i} ];

create_clock -add -name sys_clk_pin -period 10.00 -waveform {0 5} [get_ports {clk_i}];

#########################################################################################

# RESET in real lab:

set_property -dict { PACKAGE_PIN N17 IOSTANDARD LVCMOS33 } [get_ports {rst_i} ]; # BTNC

#########################################################################################

# RESET in remote lab:

set_property -dict { PACKAGE_PIN H14 IOSTANDARD LVCMOS33 } [get_ports {rst_i} ]; #SW0

########################################################################################

# BUTTONS in real lab:

#set_property -dict { PACKAGE_PIN P18 IOSTANDARD LVCMOS33 } [get_ports { button_i[1] }]; # BTND

#set_property -dict { PACKAGE_PIN P17 IOSTANDARD LVCMOS33 } [get_ports { button_i[2] }]; # BTNL

#set_property -dict { PACKAGE_PIN M17 IOSTANDARD LVCMOS33 } [get_ports { button_i[3] }]; # BTNR

#########################################################################################

set_property -dict { PACKAGE_PIN H17 IOSTANDARD LVCMOS33 } [get_ports { led_o[0] }]; # LED0

set_property -dict { PACKAGE_PIN K15 IOSTANDARD LVCMOS33 } [get_ports { led_o[1] }]; # LED1

set_property -dict { PACKAGE_PIN J13 IOSTANDARD LVCMOS33 } [get_ports { led_o[2] }]; # LED2

set_property -dict { PACKAGE_PIN N14 IOSTANDARD LVCMOS33 } [get_ports { led_o[3] }]; # LED3

set_property -dict { PACKAGE_PIN R18 IOSTANDARD LVCMOS33 } [get_ports { led_o[4] }]; # LED4

set_property -dict { PACKAGE_PIN V17 IOSTANDARD LVCMOS33 } [get_ports { led_o[5] }]; # LED5

set_property -dict { PACKAGE_PIN U17 IOSTANDARD LVCMOS33 } [get_ports { led_o[6] }]; # LED6

set_property -dict { PACKAGE_PIN U16 IOSTANDARD LVCMOS33 } [get_ports { led_o[7] }]; # LED7

#########################################################################################

set_property -dict { PACKAGE_PIN R12 IOSTANDARD LVCMOS33 } [get_ports { led_clk_o }]; # LED_RGB

# Voltage supply for the configuration interfaces on board:

set_property CFGBVS VCCO [current_design]

set_property CONFIG_VOLTAGE 3.3 [current_design]

#########################################################################################

After starting the system, the blue LED signals the 1Hz clock, and the LD0-LD7 diodes show the output status of the OUT_PORT port.

2. Basic version of the system with the Picoblaze processor

The basic version (Fig.2) should operate according to the following assumptions:

- After the reset, the display should display "0000".

- For simplicity, we assume that only 1 digit (the least significant), displayed in hexadecimal form, is subject to regulation.

- Pressing the BTNU button should increase the displayed value by 1, e.g. "0000" -->"0001".

- Pressing the BTND button should decrease the displayed value by 1, e.g. "000a" -->"0009".

- When overflowed, the counter should roll over, i.e. "000f" + 1 --> "0000", "0000" - 1 --> "000f".

- It is necessary to protect yourself against vibration of the buttons and control the release of the buttons.

- The Picoblaze processor must be clocked at 1 kHz.

- Connect the reset to the BTNC switch.

- The Picoblaze processor has a synchronous reset input - reset occurs when the reset pin is high and when the rising edge of the clock occurs.

3. Advanced version of the system with the Picoblaze processor

Enhance the base project with the following features:

- There are two working modes: display mode and edit mode.

- By default, the display only displays the entered values without the possibility of setting (display mode), but after a long press of the BTNR button (e.g. for more than 0.5 sec.), the edit mode is entered, where we can change the digit values using the BTNU and BTND buttons. The currently set digit should be blinking.

- Setting all digits, not just one (BTNL and BTNR buttons can be used to change which digit is adjusted).

- Exit from edit mode - also by long pressing the BTNR button.

XDC file, Nexys7 board, version for stationary and remote implementation (note: appropriate lines must be deleted!):

#########################################################################################

# CLOCK:

set_property -dict { PACKAGE_PIN E3 IOSTANDARD LVCMOS33 } [get_ports {clk_i} ];

create_clock -add -name sys_clk_pin -period 10.00 -waveform {0 5} [get_ports {clk_i}];

#########################################################################################

# RESET in real lab:

set_property -dict { PACKAGE_PIN N17 IOSTANDARD LVCMOS33 } [get_ports {rst_i} ]; # BTNC

#########################################################################################

# RESET in remote lab:

set_property -dict { PACKAGE_PIN H14 IOSTANDARD LVCMOS33 } [get_ports {rst_i} ]; #SW0

########################################################################################

# BUTTONS in real lab:

set_property -dict { PACKAGE_PIN M18 IOSTANDARD LVCMOS33 } [get_ports { button_i[0] }]; # BTNU

set_property -dict { PACKAGE_PIN P18 IOSTANDARD LVCMOS33 } [get_ports { button_i[1] }]; # BTND

set_property -dict { PACKAGE_PIN P17 IOSTANDARD LVCMOS33 } [get_ports { button_i[2] }]; # BTNL

set_property -dict { PACKAGE_PIN M17 IOSTANDARD LVCMOS33 } [get_ports { button_i[3] }]; # BTNR

#########################################################################################

# BUTTONS in remote lab:

set_property -dict { PACKAGE_PIN C17 IOSTANDARD LVCMOS33 } [get_ports { button_i[0] }]; # BTN0

set_property -dict { PACKAGE_PIN D18 IOSTANDARD LVCMOS33 } [get_ports { button_i[1] }]; # BTN1

set_property -dict { PACKAGE_PIN E18 IOSTANDARD LVCMOS33 } [get_ports { button_i[2] }]; # BTN2

set_property -dict { PACKAGE_PIN G17 IOSTANDARD LVCMOS33 } [get_ports { button_i[3] }]; # BTN3

#########################################################################################

# LED 7-SEGMENT DISPLAY:

set_property -dict { PACKAGE_PIN T10 IOSTANDARD LVCMOS33 } [get_ports { led7_seg_o[7] }];

set_property -dict { PACKAGE_PIN R10 IOSTANDARD LVCMOS33 } [get_ports { led7_seg_o[6] }];

set_property -dict { PACKAGE_PIN K16 IOSTANDARD LVCMOS33 } [get_ports { led7_seg_o[5] }];

set_property -dict { PACKAGE_PIN K13 IOSTANDARD LVCMOS33 } [get_ports { led7_seg_o[4] }];

set_property -dict { PACKAGE_PIN P15 IOSTANDARD LVCMOS33 } [get_ports { led7_seg_o[3] }];

set_property -dict { PACKAGE_PIN T11 IOSTANDARD LVCMOS33 } [get_ports { led7_seg_o[2] }];

set_property -dict { PACKAGE_PIN L18 IOSTANDARD LVCMOS33 } [get_ports { led7_seg_o[1] }];

set_property -dict { PACKAGE_PIN H15 IOSTANDARD LVCMOS33 } [get_ports { led7_seg_o[0] }];

set_property -dict { PACKAGE_PIN J17 IOSTANDARD LVCMOS33 } [get_ports { led7_an_o[0] }];

set_property -dict { PACKAGE_PIN J18 IOSTANDARD LVCMOS33 } [get_ports { led7_an_o[1] }];

set_property -dict { PACKAGE_PIN T9 IOSTANDARD LVCMOS33 } [get_ports { led7_an_o[2] }];

set_property -dict { PACKAGE_PIN J14 IOSTANDARD LVCMOS33 } [get_ports { led7_an_o[3] }];

set_property -dict { PACKAGE_PIN P14 IOSTANDARD LVCMOS33 } [get_ports { led7_an_o[4] }];

set_property -dict { PACKAGE_PIN T14 IOSTANDARD LVCMOS33 } [get_ports { led7_an_o[5] }];

set_property -dict { PACKAGE_PIN K2 IOSTANDARD LVCMOS33 } [get_ports { led7_an_o[6] }];

set_property -dict { PACKAGE_PIN U13 IOSTANDARD LVCMOS33 } [get_ports { led7_an_o[7] }];

#########################################################################################

set_property -dict { PACKAGE_PIN H17 IOSTANDARD LVCMOS33 } [get_ports { leds_o[0] }];

set_property -dict { PACKAGE_PIN K15 IOSTANDARD LVCMOS33 } [get_ports { leds_o[1] }];

set_property -dict { PACKAGE_PIN J13 IOSTANDARD LVCMOS33 } [get_ports { leds_o[2] }];

set_property -dict { PACKAGE_PIN N14 IOSTANDARD LVCMOS33 } [get_ports { leds_o[3] }];

set_property -dict { PACKAGE_PIN R18 IOSTANDARD LVCMOS33 } [get_ports { leds_o[4] }];

set_property -dict { PACKAGE_PIN V17 IOSTANDARD LVCMOS33 } [get_ports { leds_o[5] }];

set_property -dict { PACKAGE_PIN U17 IOSTANDARD LVCMOS33 } [get_ports { leds_o[6] }];

set_property -dict { PACKAGE_PIN U16 IOSTANDARD LVCMOS33 } [get_ports { leds_o[7] }];

#########################################################################################

Attention

The Picoblaze processor has a synchronous reset input: reset occurs when the reset pin is high and when the rising edge of the clk clock occurs.