Lab 0: Procesor Picoblaze

Wstęp

Celem ćwiczenia jest opracowanie systemu mikroelektronicznego z procesorem Picoblaze, w którym część sprzętowa realizuje dzielenie częstotliwości zegara oraz multipleksowane wyświetlanie na wyświetlaczu LED. Do zadań oprogramowania należy odczyt przycisków i w zależności od tego zwiększanie lub zmniejszanie licznika i wysłanie tej informacji na wyświetlacz LED.

1. Wersja startowa systemu z procesorem Picoblaze

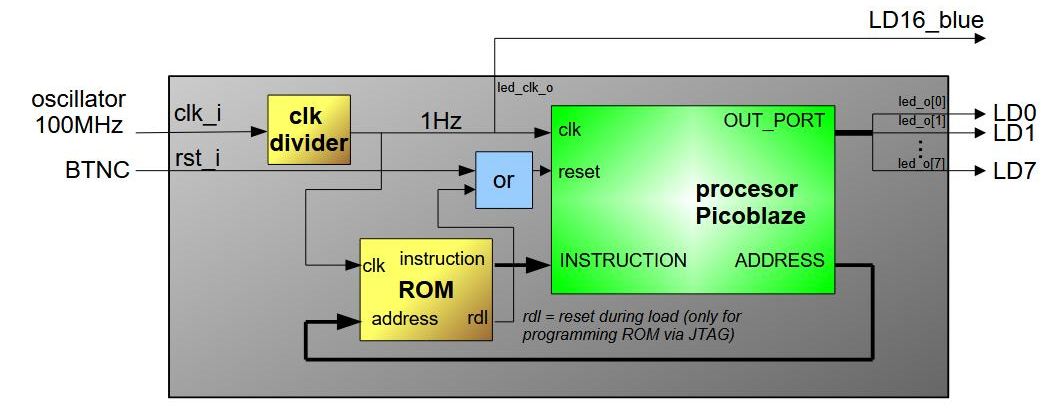

W pierwszym kroku należy zrealizować uproszczony system wg schematu blokowego:

Rys. 1 Schemat blokowy wersji startowej systemu.

Zegar clk_i z oscylatora 100MHz należy podzielić tak, aby otrzymać zegar clk dla procesora Picoblaze o częstotliwości 1Hz.

Program asemblera:

LOAD sA, fE ; write initial value: 11111110

START: OUTPUT sA, 00 ; Write sA to OUT_PORT

RL sA ; rotate register sA, i.e. 11111110 -> 11111101

JUMP START ; Jump to beginning (infinite loop)

Osadzając pamięć ROM z programem w asemblerze, należy ustawić parametr generic informujący o tym, że pamięć będzie realizowana w układzie FPGA z rodziny Virtex-6 (dot. płytki Nexys7):

C_FAMILY => "V6"

Plik XDC, płytka Nexys7, wersja dla realizacji stacjonarnej i zdalnej (uwaga: należy usunąć odpowiednie linie!):

#########################################################################################

# CLOCK:

set_property -dict { PACKAGE_PIN E3 IOSTANDARD LVCMOS33 } [get_ports {clk_i} ];

create_clock -add -name sys_clk_pin -period 10.00 -waveform {0 5} [get_ports {clk_i}];

#########################################################################################

# RESET in real lab:

set_property -dict { PACKAGE_PIN N17 IOSTANDARD LVCMOS33 } [get_ports {rst_i} ]; # BTNC

#########################################################################################

# RESET in remote lab:

set_property -dict { PACKAGE_PIN H14 IOSTANDARD LVCMOS33 } [get_ports {rst_i} ]; #SW0

########################################################################################

# BUTTONS in real lab:

#set_property -dict { PACKAGE_PIN P18 IOSTANDARD LVCMOS33 } [get_ports { button_i[1] }]; # BTND

#set_property -dict { PACKAGE_PIN P17 IOSTANDARD LVCMOS33 } [get_ports { button_i[2] }]; # BTNL

#set_property -dict { PACKAGE_PIN M17 IOSTANDARD LVCMOS33 } [get_ports { button_i[3] }]; # BTNR

#########################################################################################

set_property -dict { PACKAGE_PIN H17 IOSTANDARD LVCMOS33 } [get_ports { led_o[0] }]; # LED0

set_property -dict { PACKAGE_PIN K15 IOSTANDARD LVCMOS33 } [get_ports { led_o[1] }]; # LED1

set_property -dict { PACKAGE_PIN J13 IOSTANDARD LVCMOS33 } [get_ports { led_o[2] }]; # LED2

set_property -dict { PACKAGE_PIN N14 IOSTANDARD LVCMOS33 } [get_ports { led_o[3] }]; # LED3

set_property -dict { PACKAGE_PIN R18 IOSTANDARD LVCMOS33 } [get_ports { led_o[4] }]; # LED4

set_property -dict { PACKAGE_PIN V17 IOSTANDARD LVCMOS33 } [get_ports { led_o[5] }]; # LED5

set_property -dict { PACKAGE_PIN U17 IOSTANDARD LVCMOS33 } [get_ports { led_o[6] }]; # LED6

set_property -dict { PACKAGE_PIN U16 IOSTANDARD LVCMOS33 } [get_ports { led_o[7] }]; # LED7

#########################################################################################

set_property -dict { PACKAGE_PIN R12 IOSTANDARD LVCMOS33 } [get_ports { led_clk_o }]; # LED_RGB

# Voltage supply for the configuration interfaces on board:

set_property CFGBVS VCCO [current_design]

set_property CONFIG_VOLTAGE 3.3 [current_design]

#########################################################################################

Po uruchomieniu systemu, niebieska dioda LED sygnalizuje nam prqacę zegara 1Hz, a diody LD0-LD7 pokazują stan wyjścia portu OUT_PORT.

2. Wersja podstawowa systemu z procesorem Picoblaze

Wersja podstawowa (Rys.2) powinna działać wg następujących założeń:

- Zmieniamy częstotliwość zegara procesora z 1Hz na 1kHz.

- Po resecie wyświetlacz powinien wyświetlić "0000".

- Dla uproszczenia zakładamy, że regulacji podlega tylko 1 cyfra (najmniej znacząca), wyświetlana w postaci szesnastkowej.

- Naciśnięcie przycisku BTNU powinno zwiększać o 1 wyświetlaną wartość, np. "0000" -->"0001".

- Naciśnięcie przycisku BTND powinno zmniejszać o 1 wyświetlaną wartość, np. "000a" -->"0009".

- Po przepełnieniu licznik powinien się przekręcać, tj. "000f" + 1 --> "0000", "0000" - 1 --> "000f".

- Należy w podstawowym zakresie zabezpieczyć się przed drganiami przycisków oraz kontrolować puszczenie przycisków.

- Procesor Picoblaze należy taktować zegarem o częstotliwości 1 kHz.

- Reset podłączyć do przełącznika BTNC.

- Procesor Picoblaze posiada synchroniczne wejście resetu - reset następuje w przypadku wysokiego stanu na końcówce reset oraz przy wystąpieniu narastającego zbocza zegara.

3. Wersja zaawansowana systemu z procesorem Picoblaze

Wzbogacić projekt podstawowy o tryb edycji, w któym możemy ustawić dowolną liczbę na 4-cyfrowym wyswietlaczu.

Dokładny opis wymaganej funkcjonalności:

- Mamy dwa tryby pracy: tryb wyświetlania i edycji.

- Po resecie wyświetlacz powinien wyświetlić "0000" i przejść do trybu wyświetlania.

- Po dłuższym naciśnięciu przycisku BTNR (np. przez ponad 0.5 sek.) następuje wejście do trybu edycji, gdzie możemy przyciskami BTNU i BTND zmieniać wartości pojedynczej cyfry. Przyciskami BTNL i BTNR można zmieniać, która cyfra podlega regulacji.

- Aktualnie ustawiana cyfra powinna mrugać.

- Wyjście z trybu edycji - także przez dłuższe naciśnięcie przycisku BTNR.

Plik XDC do zadania, płytka Nexys A7, wersja dla realizacji stacjonarnej i zdalnej (uwaga: należy usunąć odpowiednie linie!):

#########################################################################################

# CLOCK:

set_property -dict { PACKAGE_PIN E3 IOSTANDARD LVCMOS33 } [get_ports {clk_i} ];

create_clock -add -name sys_clk_pin -period 10.00 -waveform {0 5} [get_ports {clk_i}];

#########################################################################################

# RESET in real lab:

set_property -dict { PACKAGE_PIN N17 IOSTANDARD LVCMOS33 } [get_ports {rst_i} ]; # BTNC

#########################################################################################

# RESET in remote lab:

set_property -dict { PACKAGE_PIN H14 IOSTANDARD LVCMOS33 } [get_ports {rst_i} ]; #SW0

########################################################################################

# BUTTONS in real lab:

set_property -dict { PACKAGE_PIN M18 IOSTANDARD LVCMOS33 } [get_ports { button_i[0] }]; # BTNU

set_property -dict { PACKAGE_PIN P18 IOSTANDARD LVCMOS33 } [get_ports { button_i[1] }]; # BTND

set_property -dict { PACKAGE_PIN P17 IOSTANDARD LVCMOS33 } [get_ports { button_i[2] }]; # BTNL

set_property -dict { PACKAGE_PIN M17 IOSTANDARD LVCMOS33 } [get_ports { button_i[3] }]; # BTNR

#########################################################################################

# BUTTONS in remote lab:

set_property -dict { PACKAGE_PIN C17 IOSTANDARD LVCMOS33 } [get_ports { button_i[0] }]; # BTN0

set_property -dict { PACKAGE_PIN D18 IOSTANDARD LVCMOS33 } [get_ports { button_i[1] }]; # BTN1

set_property -dict { PACKAGE_PIN E18 IOSTANDARD LVCMOS33 } [get_ports { button_i[2] }]; # BTN2

set_property -dict { PACKAGE_PIN G17 IOSTANDARD LVCMOS33 } [get_ports { button_i[3] }]; # BTN3

#########################################################################################

# LED 7-SEGMENT DISPLAY:

set_property -dict { PACKAGE_PIN T10 IOSTANDARD LVCMOS33 } [get_ports { led7_seg_o[7] }];

set_property -dict { PACKAGE_PIN R10 IOSTANDARD LVCMOS33 } [get_ports { led7_seg_o[6] }];

set_property -dict { PACKAGE_PIN K16 IOSTANDARD LVCMOS33 } [get_ports { led7_seg_o[5] }];

set_property -dict { PACKAGE_PIN K13 IOSTANDARD LVCMOS33 } [get_ports { led7_seg_o[4] }];

set_property -dict { PACKAGE_PIN P15 IOSTANDARD LVCMOS33 } [get_ports { led7_seg_o[3] }];

set_property -dict { PACKAGE_PIN T11 IOSTANDARD LVCMOS33 } [get_ports { led7_seg_o[2] }];

set_property -dict { PACKAGE_PIN L18 IOSTANDARD LVCMOS33 } [get_ports { led7_seg_o[1] }];

set_property -dict { PACKAGE_PIN H15 IOSTANDARD LVCMOS33 } [get_ports { led7_seg_o[0] }];

set_property -dict { PACKAGE_PIN J17 IOSTANDARD LVCMOS33 } [get_ports { led7_an_o[0] }];

set_property -dict { PACKAGE_PIN J18 IOSTANDARD LVCMOS33 } [get_ports { led7_an_o[1] }];

set_property -dict { PACKAGE_PIN T9 IOSTANDARD LVCMOS33 } [get_ports { led7_an_o[2] }];

set_property -dict { PACKAGE_PIN J14 IOSTANDARD LVCMOS33 } [get_ports { led7_an_o[3] }];

set_property -dict { PACKAGE_PIN P14 IOSTANDARD LVCMOS33 } [get_ports { led7_an_o[4] }];

set_property -dict { PACKAGE_PIN T14 IOSTANDARD LVCMOS33 } [get_ports { led7_an_o[5] }];

set_property -dict { PACKAGE_PIN K2 IOSTANDARD LVCMOS33 } [get_ports { led7_an_o[6] }];

set_property -dict { PACKAGE_PIN U13 IOSTANDARD LVCMOS33 } [get_ports { led7_an_o[7] }];

#########################################################################################

set_property -dict { PACKAGE_PIN H17 IOSTANDARD LVCMOS33 } [get_ports { leds_o[0] }];

set_property -dict { PACKAGE_PIN K15 IOSTANDARD LVCMOS33 } [get_ports { leds_o[1] }];

set_property -dict { PACKAGE_PIN J13 IOSTANDARD LVCMOS33 } [get_ports { leds_o[2] }];

set_property -dict { PACKAGE_PIN N14 IOSTANDARD LVCMOS33 } [get_ports { leds_o[3] }];

set_property -dict { PACKAGE_PIN R18 IOSTANDARD LVCMOS33 } [get_ports { leds_o[4] }];

set_property -dict { PACKAGE_PIN V17 IOSTANDARD LVCMOS33 } [get_ports { leds_o[5] }];

set_property -dict { PACKAGE_PIN U17 IOSTANDARD LVCMOS33 } [get_ports { leds_o[6] }];

set_property -dict { PACKAGE_PIN U16 IOSTANDARD LVCMOS33 } [get_ports { leds_o[7] }];

#########################################################################################

Uwaga

Procesor Picoblaze posiada synchroniczne wejście resetu: reset następuje w przypadku wysokiego stanu na końcówce reset oraz przy wystąpieniu narastającego zbocza zegara clk.